8XC251SA, SB, SP, SQ USER’S MANUAL

14-4

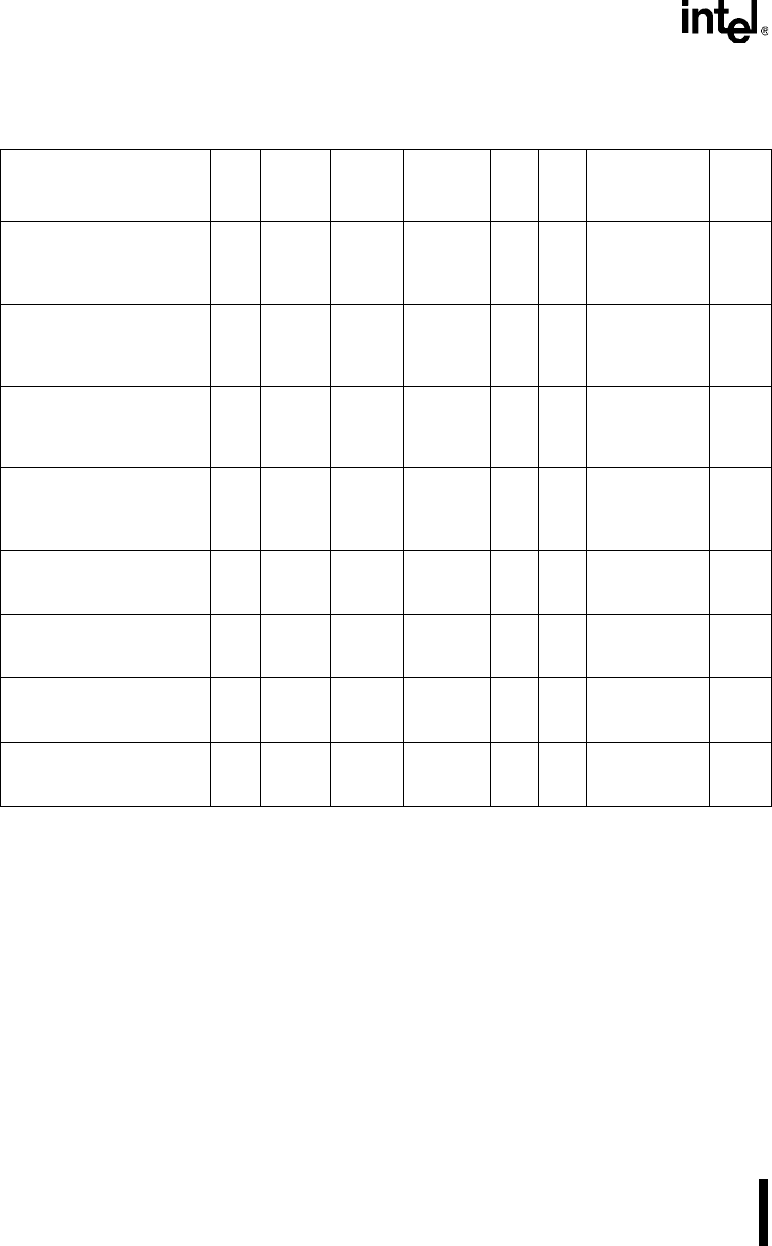

Table 14-1. Programming and Verifying Modes

Mode RST PSEN# V

PP

PROG# Port

0

Port

2

Address

Port 1 (high)

Port 3 (low)

Notes

Program Mode. On-chip

Code Memory

8K 87C251SA,SP

16K 87C251SB,SQ

High Low 5 V,

12.75 V

5 Pulses 68H data

0000H-1FFFH

0000H-3FFFH

1, 4

Verify Mode. On-chip

Code Memory

8K 87/83C251SA,SP

16K 87/83C251SB,SQ

High Low 5 V High 28H data

0000H-1FFFH

0000H-3FFFH

4

Program Mode. Configu-

ration Bytes (UCONFIG0,

UCONFIG1)

87C251S

x

High Low 5 V,

12.75 V

5 Pulses 69H data FFF8H-FFFFH 1, 4

Verify Mode. Configuration

Bytes (UCONFIG0,

UCONFIG1)

8XC251S

x

High Low 5 V High 29H data FFF8H-FFFFH 4

Program Mode. Lock Bits

87C251S

x

High Low 5 V,

12.75 V

25 Pulses 6BH data 0001H-0003H 1, 2

Verify Mode. Lock bits

87C251S

x

, 83C251S

x

High Low 5 V High 2BH data 0000H 3

Program Mode. Encryption

Array

87C251S

x

High Low 5 V,

12.75 V

25 Pulses 6CH data 0000H-007FH 1

Verify Mode. Signature

Bytes

87C251S

x

, 83C251S

x

High Low 5 V High 29H data 0030H,0031H,

0060H,

0061H

NOTES:

1. To program, raise V

PP

to 12.75 V and pulse the PROG# pin. See Figure 14-2 for waveforms.

2. No data input. Identify the lock bits with the address lines as follows: LB3 - 0003H, LB2 - 0002H,

LB1 - 0001H.

3. The three lock bits are verified in a single operation. The states of the lock bits appear simultaneously

at port 2 as follows: LB3 - P2.3, LB2 - P2.2. LB1 - P2.1. High = programmed.

4. For these modes, the internal address is FF:

xxxx

H.