A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

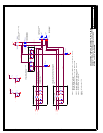

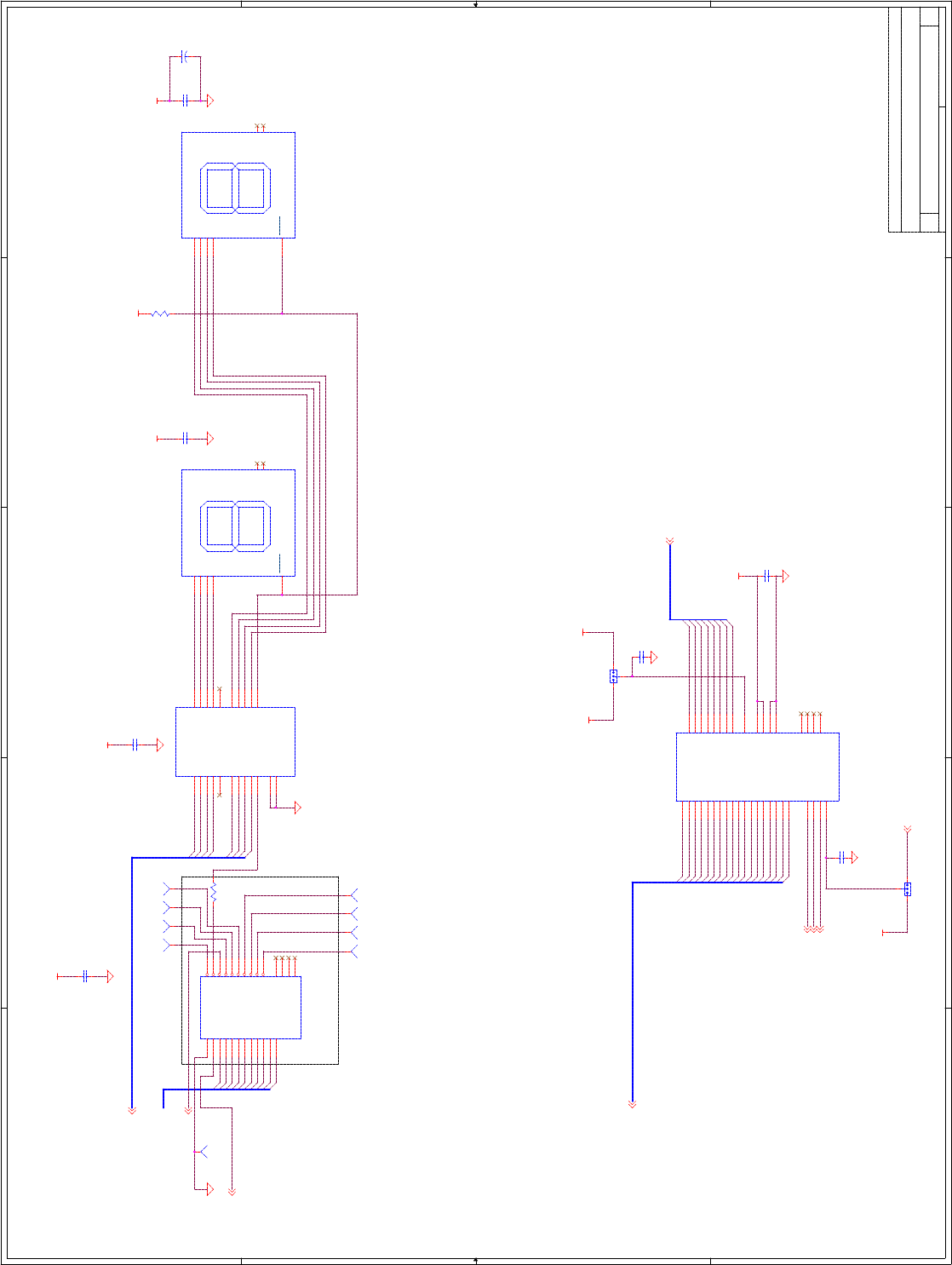

Expect All 0's except

SA7=1 for P80 Decode

Standard

Stuff

Option

Port 80

THIS DRAWING CONTAINS INFORMATION WHICH HAS NOT

BEEN VERIFIED FOR MANUFACTURING AS AN END USER

PRODUCT. INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

{Doc}

D

BIOS/ Port 80

C

20 22Thursday, February 25, 1999

Title

Size Document Number Rev

Date: Sheet of

SD[15:0]

SA[19:0]

SD4

SD5

SD6

SD7

SD0

SD1

SD2

SD3

SA4

SA1

SA9

SA0

SA5

SA3

SA2

SA6

SA7

SA8

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

XD0

XD1

XD2

XD3

XD4

XD5

XD6

XD7

SA17

SD[15:0]9,13,16,18

IOW#9,13,16,18

AEN13,16,18

SA[19:0]9,13,16,18

XD[7:0] 13

MEMW#9,13,18

MEMR#9,13,18

BIOSCS#14

PWROK5 21

V5_0

V5_0

V5_0

V5_0 V5_0

V5_0

+12V

+12V

V5_0

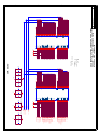

U10

QST3384

3

4

7

8

14

17

18

21

11

22

2

5

6

9

10

15

16

19

20

23

12

24

1

13

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1A5

2A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

GND

V5_0

BEA

BEB

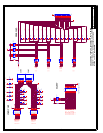

U13

TIL311 SOCKET

14

1

7

8

5

3

2

13

12

10

4

V5_0

V5_0

GND

GND

LATCH

A

B

C

D

RTDEC

LFTDEC

U12

TIL311 SOCKET

14

1

7

8

5

3

2

13

12

10

4

V5_0

V5_0

GND

GND

LATCH

A

B

C

D

RTDEC

LFTDEC

U9

22V10

1

8

17

15

22

2

183

194

205

216

237

249

2510

2611

2712

13

16

NC

NC

O1

NC

NC

I1/CLK

O2I2

O3I3

O4I4

O5I5

O6I6

O7I7

O8I8

O9I9

O10I10

I11

I12

U11

28F002BC

12

31

139

37

30

38

25

39

24

23

21

22

26

10

20

27

19

28

18

32

17

33

16

34

15

35

14

8

7

36

6

5

4

3

2

1

40

11

NC

VCC

NCWE#

NC

VCC

NC

DQ0

GND

OE#

GND

A0

CE#

DQ1

RP#

A1

DQ2

A2

DQ3

A3

DQ4

A4

DQ5

A5

DQ6

A6

DQ7

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

VPP

C196

0.1uF

C200

0.1uF

C206

0.1uF

C205

0.1uF

C208

0.1uF

C131

0.1uF

C130

0.1uF

R105

10K

R98

0

C145

10uF

J22

HDR3

1

2

3

J21

1x3

1

2

3

TP8

1

TP

TP14

1

TP

TP2

1

TP

TP7

1

TP

TP6

1

TP

TP16

1

TP

TP10

1

TP

TP9

1

TP

TP12

1

TP