A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

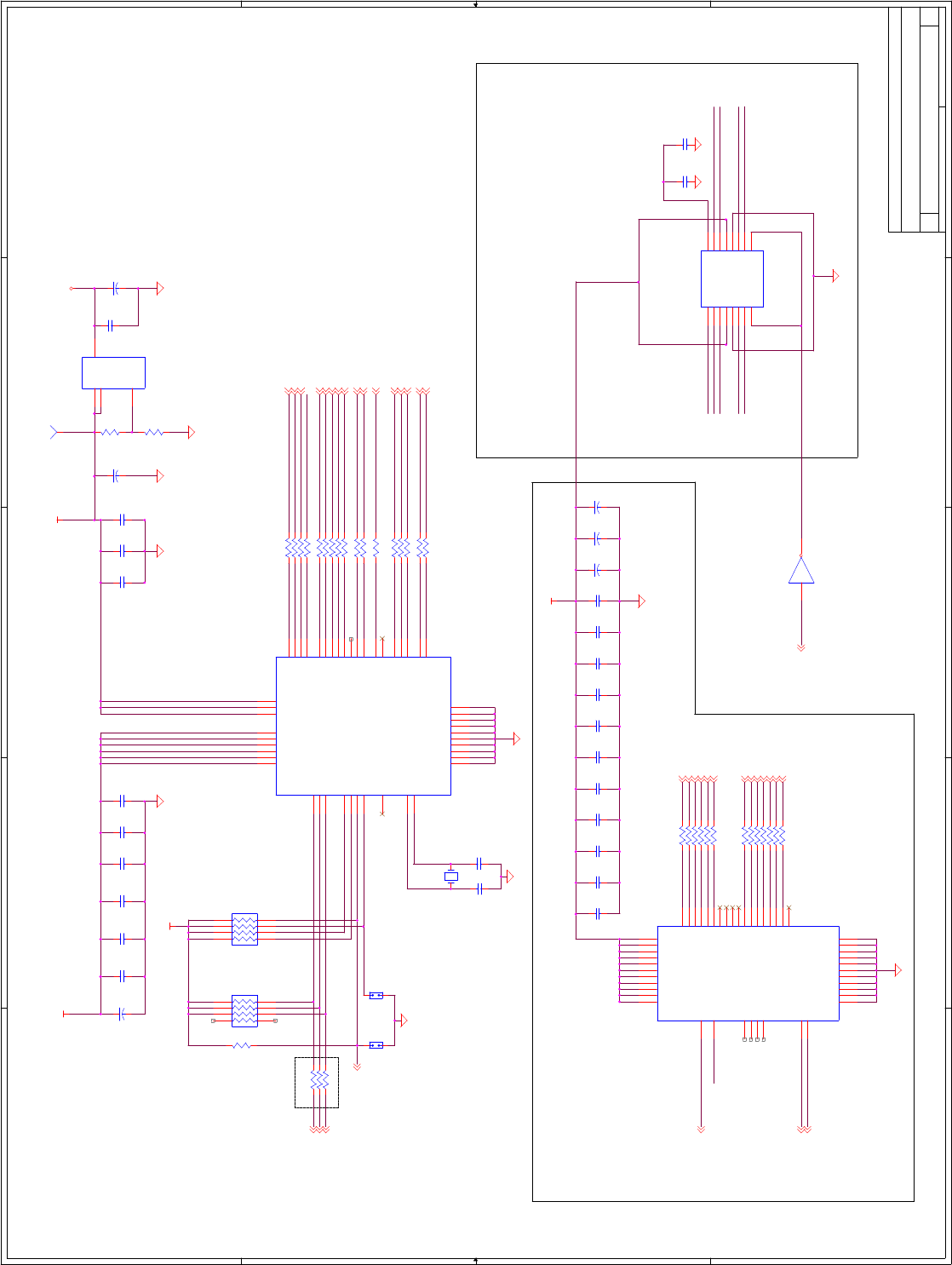

Stuff only to enable

stopping of clocks

This circuit is only used for

TX/Pentium Designs. Note only

two DIMMS are supported.

This circuit is only used for

BX/PentiumII Designs. Note

three DIMMS are supported.

These caps can be tuned to

change delay through buffer.

Keep crystal close to clock and

caps close to crystal. All lead

lengths should be equal.

Note: R11 and R12 should be placed as

close as possible to U1

1%

1%

THIS DRAWING CONTAINS INFORMATION WHICH HAS NOT

BEEN VERIFIED FOR MANUFACTURING AS AN END USER

PRODUCT. INTEL IS NOT RESPONSIBLE FOR THE

MISUSE OF THIS INFORMATION.

{Doc}

D

Clocks

C

8 22Thursday, February 25, 1999

Title

Size Document Number Rev

Date: Sheet of

CPUCLKR_0

CPUCLKR_1

CPUCLKR_2

CPUCLKR_3 CPUCLK3

PCICLKF_R

PCICLKR_1

PCICLKR_2

PCICLKR_3

PCICLKR_4

PCICLKR_6

PCICLKR_7

USBCLKR_0

REFR_0

REFR_1

REFR_2

APICCLKR_0

APICCLKR_1

V2.5

CONFIG1 SDCLKR0

SDCLKR1

SDCLKR2

SDCLKR4

SDCLKR6

SDCLKR7

CONFIG1#

SDCLKR3

SDCLKR0

SDCLKR1

SDCLKR2

SDCLKR3

SDCLKR10

SDCLKR11

SDCLKR5

CPUCLK3SDCLKR8

SDCLKR9

SDCLKR7

SDCLKR6

SDCLKR4

SDCLKR5

CPUCLK1 4

CPUCLK0 4

CPUCLK2 4

PCICLKF 14

PCICLK1 10

PCICLK2 10

PCICLK3 11

PCICLK4 3

PCLKAPIC 13

PCICLK7 4

USBCLK0 14

REF0 18

REF1 16

REF2 14

APICCLK0 13

APICCLK1 4

MAB#12_R7

SMBDATA4,5,6,7,9,14

SMBCLK4,5,6,7,9,14

BXDCLKO4

SDCLK0 5

SDCLK1 5

SDCLK2 5

SDCLK3 5

SDCLK4 6

SDCLK5 6

SDCLK6 6

SDCLK8 7

SDCLK9 7

SDCLK10 7

SDCLK11 7

BxFBCLK 4

CPU_STOP#14

PCI_STOP#14

SUSA#14

CONFIG14,14

SDCLK7 6

V3_3

V5_0

V3_3

V3_3

V2.5

U6

CY2280

153

9

30

21

6

48

31

46

12

41

1

37

18

33

29

1920

7

24

2

32

40

34

47

38

8

43

39

10

36

11

35

13

14

16

17

22

23

45

44

28

27

26

25

4

5

42

VDDPCIVSS

VDDPCI

CPU_STOP#

VDDUSB

VSS

VDDREF

PCI_STOP#

VDDAPIC

VSS

VDDCPU

REF0

VDDCPU

VSS

AVDD

PWR_DWN#

AVDDVSS

PCICLK_F

VSS

REF1

VSS

CPUCLK0

VSS

REF2

VSS

PCI_CLK1

VSS

CPUCLK1

PCI_CLK2

CPUCLK2

PCI_CLK3

CPUCLK3

PCI_CLK4

PCI_CLK5

PCI_CLK6

PCI_CLK7

USBCLK0

USBCLK1

APIC0

APIC1

SEL_SS#

SEL0

SEL1

SEL100

XTALIN

XTALOUT

RESERVED

Y1

14.318MHz

1 2

C100

10pf

C99

10pf

J15

JUMP2

12

J14

HDR2

12

R24 33

R27 33

R29 33

R31 33

R23 33

R26 33

R28 33

R32 33

R30 33

R36 33

R34 33

R38 33

R18 33

R17 33

R19 33

R21 33

R22 33

R20

2.7K

C170

0.01uF

C171

0.01uF

C101

0.01uF

C168

0.01uF

C164

0.01uF

C169

0.01uF

C173

0.01uF

C165

0.01uF

C163

0.01uF

C213

0.01uF

C217

0.01uF

C223

0.01uF

C221

0.01uF

C212

0.01uF

C225

0.01uF

C220

0.01uF

C224

0.01uF

C222

0.01uF

C216

0.01uF

C211

0.01uF

R35 0

R33 0

R37 0

U21A

74HCT14

1 2

C214

10pF

R15

124

R16

124

RP20

10K

1 8

2 7

3 6

4 5

RP22

10K

1 8

2 7

3 6

4 5

R122 0

R118 0

R120 0

R121 0

R119 0

R113 0

R109 0

R111 0

R116 0

R114 0

R112 0

R110 0

U16

CY2318NZ

4

6

5

3

8

10

9

13

15

14

7

17

19

18

31

22

32

12

35

26

36

40

27

41

16

44

30

45

21

34

28

20

39

43

23

29

33

37

42

46

11

38

24

25

1

2

47

48

SDRAM0

VSS

SDRAM1

VDD

SDRAM2

VSS

SDRAM3

SDRAM4

VSS

SDRAM5

VDD

SDRAM6

VSS

SDRAM7

SDRAM8

VSS

SDRAM9

VDD

SDRAM10

VSS

SDRAM11

SDRAM12

VSS

SDRAM13

VDD

SDRAM14

VSS

SDRAM15

SDRAM16

VSS

SDRAM17

VDD

VSS

VSS

VDD

VDD

VDD

VDD

VDD

VDD

CLK_IN

OE

SDATA

SCLK

NC

NC

NC

NC

U26

Zero Delay Buffer

161

152

143

134

125

116

107

98

CLKOUTRef

CLKA4CLKA1

CLKA3CLKA2

VDDVDD

GNDGND

CLKB4CLKB1

CLKB3CLKB2

S1S2

C209

10pF

R115 0

U5

LT117

1

2 3

4

Adj/GND

Out In

OutTab

C162

0.1uF

C95

100uF

C94

10uF

C150

15uF

C148

15uF

C93

47uF

C149

15uF

TP17

1

TP