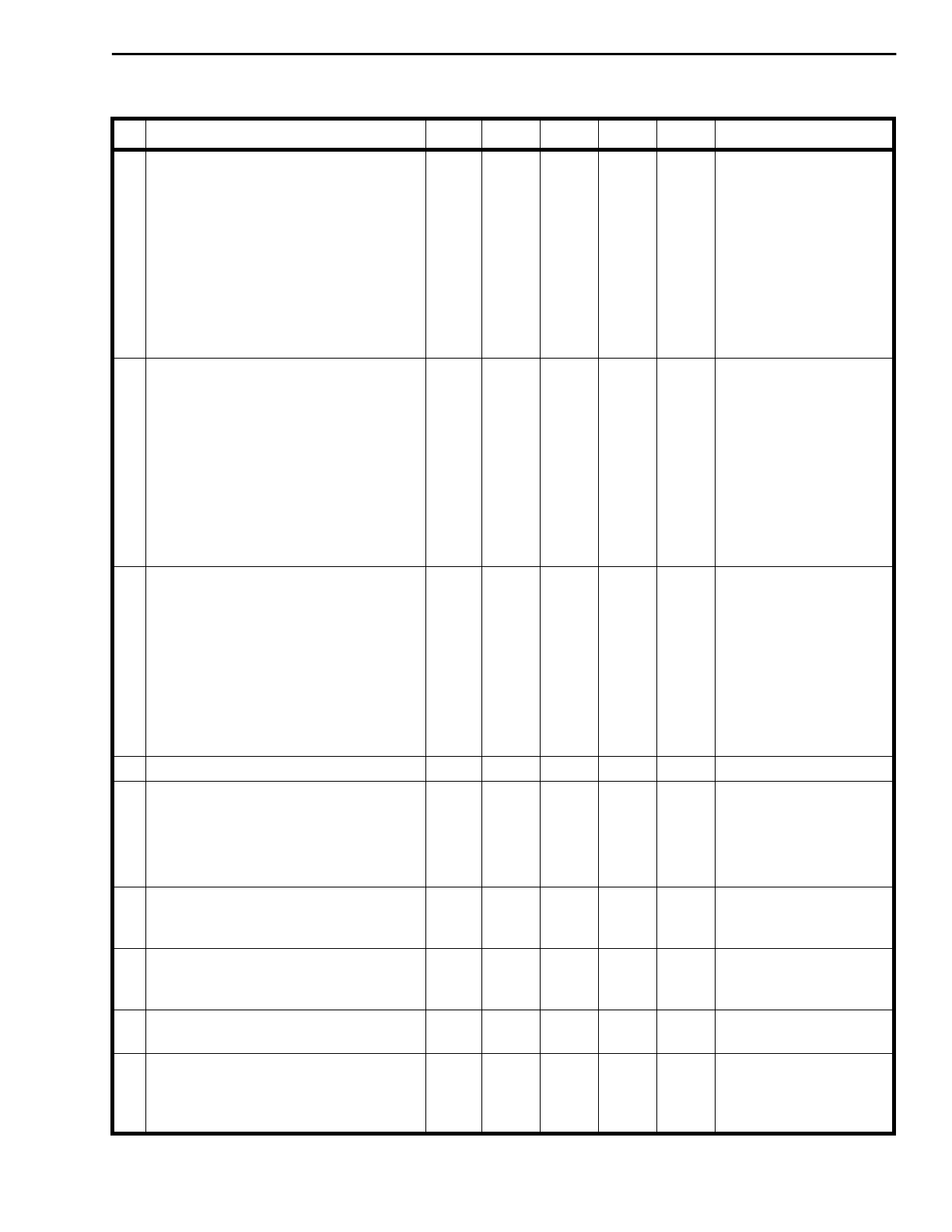

Preliminary Information MT90840

2-263

AC Electrical Characteristics - Voltages are with respect to ground (V

SS

) unless otherwise stated.

Characteristics Sym Min Typ

‡

Max Units Test Conditions

1 C4/8 Input - Clock Period:

4.096 MHz (2.048 & 4.096 Mbps)

8.192 MHz (8.192 Mbps)

SPCKo Output - Clock Period from

internal divider (2.048 & 4.096 Mbps)

SPCKo Output - Clock Period

generated from external C4/8

reference (2.048 and 4.096 Mbps)

t

clk

200

100

224

241

244

122

259

245

ns

ns

ns

ns

C4/8R1 or C4/8R2

19.44 MHz 60/40%

duty-cycle clock at

PCKR

C4/8R1 input with 244 ns

cycle

2 C4/8 Input Clock Width HIGH

4.096 MHz (2.048 & 4.096 Mbps)

8.192 MHz (8.192 Mbps)

SPCKo Output - Clock Width HIGH

from internal divider (2.048 & 4.096

Mbps)

SPCKo Output - Clock Width HIGH

generated from external C4/8

reference (2.048 and 4.096 Mbps)

t

clkh

85

50

101

110

122

61

135

ns

ns

ns

ns

C4/8R1 or C4/8R2

19.44 MHz 60/40%

duty-cycle clock at

PCKR

C4/8R1 input with min.

115 ns semi-cycle

3 C4/8 Input - Clock Width LOW

4.096 MHz (2.048 & 4.096 Mbps)

8.192 MHz (8.192 Mbps)

SPCKo Output - Clock Width LOW from

internal divider (2.048 & 4.096 Mbps)

SPCKo Output - Clock Width LOW

generated from external C4/8

reference (2.048 and 4.096 Mbps)

t

clkl

85

50

101

110

122

61

135

ns

ns

ns

ns

C4/8R1 or C4/8R2

PCKR with 60/40% duty

cycle

C4/8R1 input with

minimum 115 ns

half-cycle

4 CLK rise/fall time t

t

5ns

5 F0 output delay from SPCKo

(TM2 & TM3, 2.048 and 4.096 Mbps)

F0 output delay from C4/8 input

(TM2 & TM3, 8.192 Mbps)

t

df

32

51

30

46

ns

ns

C

L

=30pF

C

L

=150pF

C

L

=30pF

C

L

=150pF

6 F0i Setup Time from C4/8 input edge

TM1

TM2 with SFDI =1

t

frs

0

28

ns

ns

C4/8 falling edge

7 F0i Hold Time from C4/8 input edge

TM1

TM2 with SFDI =1

t

frh

8

0

ns

ns

C4/8 falling edge

C4/8 rising or falling

8 F0i Input Frame Pulse Width

2.048, 4.096, 8.192 Mbps

t

frw

35 ns

9 STo Delay - Active to High-Z,

2.048 and 4.096 Mbps (TM2 &TM3)

2.048 and 4.096 Mbps (TM1)

8.192 Mbps (STio0-3)

t

az

38

50

26

ns

ns

ns

C

L

=30pF, R

L

=1K