S3C8245/P8245/C8249/P8249 INTERRUPT STRUCTURE

5-3

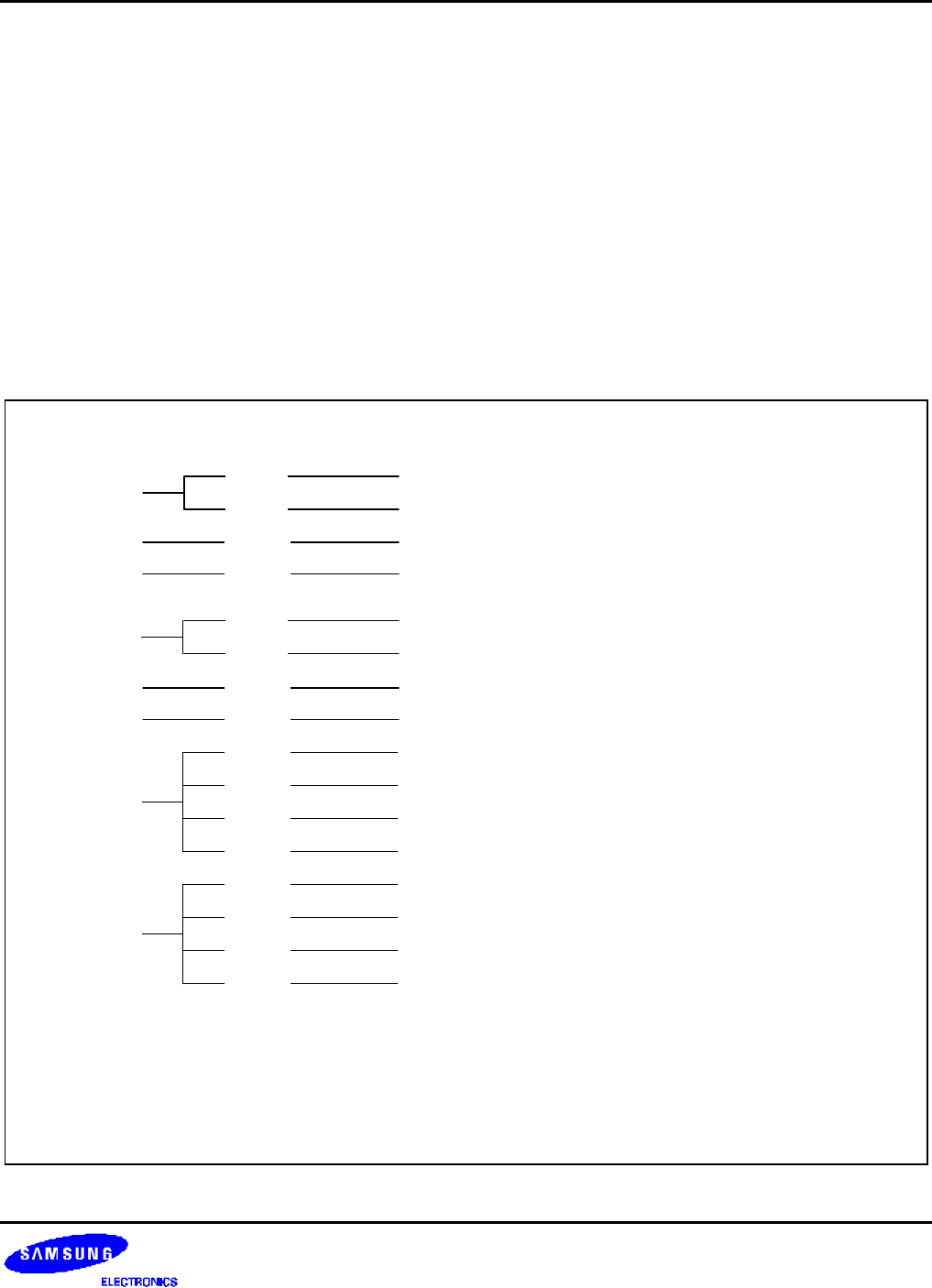

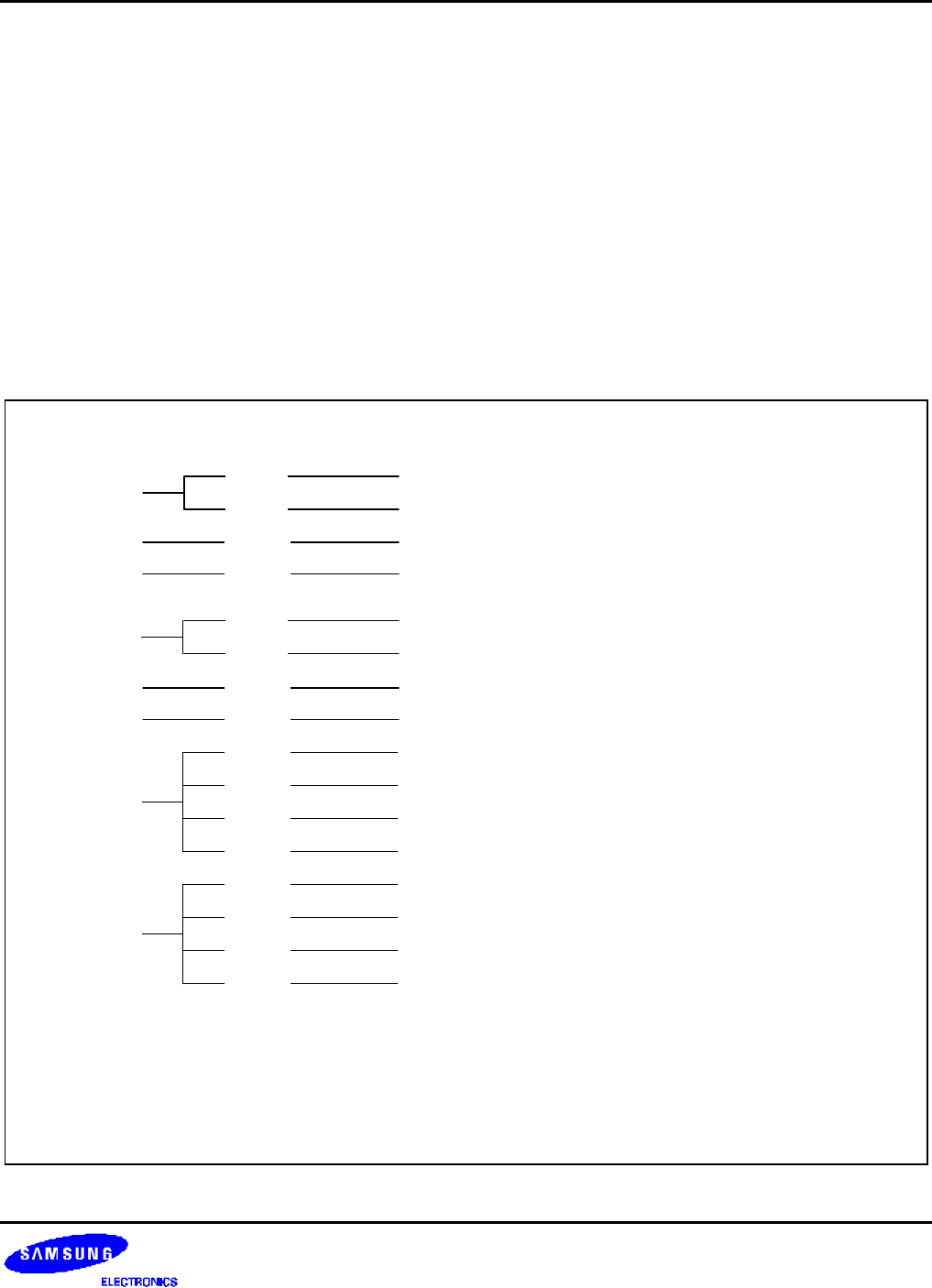

S3C8245/C8249 INTERRUPT STRUCTURE

The S3C8245/C8249 microcontroller supports sixteen interrupt sources. All sixteen of the interrupt sources have a

corresponding interrupt vector address. Eight interrupt levels are recognized by the CPU in this device-specific

interrupt structure, as shown in Figure 5-2.

When multiple interrupt levels are active, the interrupt priority register (IPR) determines the order in which contending

interrupts are to be serviced. If multiple interrupts occur within the same interrupt level, the interrupt with the lowest

vector address is usually processed first (The relative priorities of multiple interrupts within a single level are fixed in

hardware).

When the CPU grants an interrupt request, interrupt processing starts. All other interrupts are disabled and the

program counter value and status flags are pushed to stack. The starting address of the service routine is fetched

from the appropriate vector address (plus the next 8-bit value to concatenate the full 16-bit address) and the service

routine is executed.

Vectors SourcesLevels Reset/Clear

NOTES:

1. Within a given interrupt level, the low vector address has high priority.

For example, E0H has higher priority than E2H within the level IRQ.0 the priorities within each

level are set at the factory.

2. External interrupts are triggered by a rising or falling edge, depending on the corresponding control

register setting.

IRQ3

E8H Timer 1 match/capture

EAH Timer 1 overflow

Timer B match

E4H

Timer 0 match

E6H

IRQ1

IRQ2

H/W

SIO interrupt

ECH

Watch timer overflow

EEH

IRQ4

IRQ5

P0.0 external interrupt

P0.1 external interrupt

P0.2 external interrupt

P0.3 external interrupt

IRQ6

F0H

F2H

F4H

F6H

P0.4 external interrupt

P0.5 external interrupt

P0.6 external interrupt

P0.7 external interrupt

IRQ7

F8H

FAH

FCH

FEH

E0H Timer A match/capture

IRQ0

E2H Timer A overflow

H/W,S/W

H/W,S/W

H/W,S/W

H/W,S/W

H/W,S/W

S/W

S/W

S/W

S/W

S/W

S/W

S/W

S/W

S/W

S/W

Figure 5-2. S3C8245/C8249 Interrupt Structure