28 www.xilinx.com Endpoint Block Plus v1.8 for PCI Express

UG343 June 27, 2008

Chapter 3: Quickstart Example Design

R

simulation/functional

The functional directory contains the dual core example design simulation scripts.

<component name>/implement

The implement directory contains the dual core example design implementation script

files.

Simulation and implementation commands for the dual core example design are similar to

the single core example design commands. To modify simulation and implementation

commands for the dual core example design, see “Simulating the Example Design,” page

18, and “Implementing the Example Design,” page 19 and replace them with the respective

dual core names.

The simulation test bench used with the dual core example design makes use of the

downstream port TLP generator from the example design. Because the test bench has only

one downstream port, only one of the two PCI Express Block cores can be sent TLPs per

simulation run. The downstream port simulates the primary PCI Express Block core by

default. To simulate the secondary PCI Express block, you can modify board.v[hd].

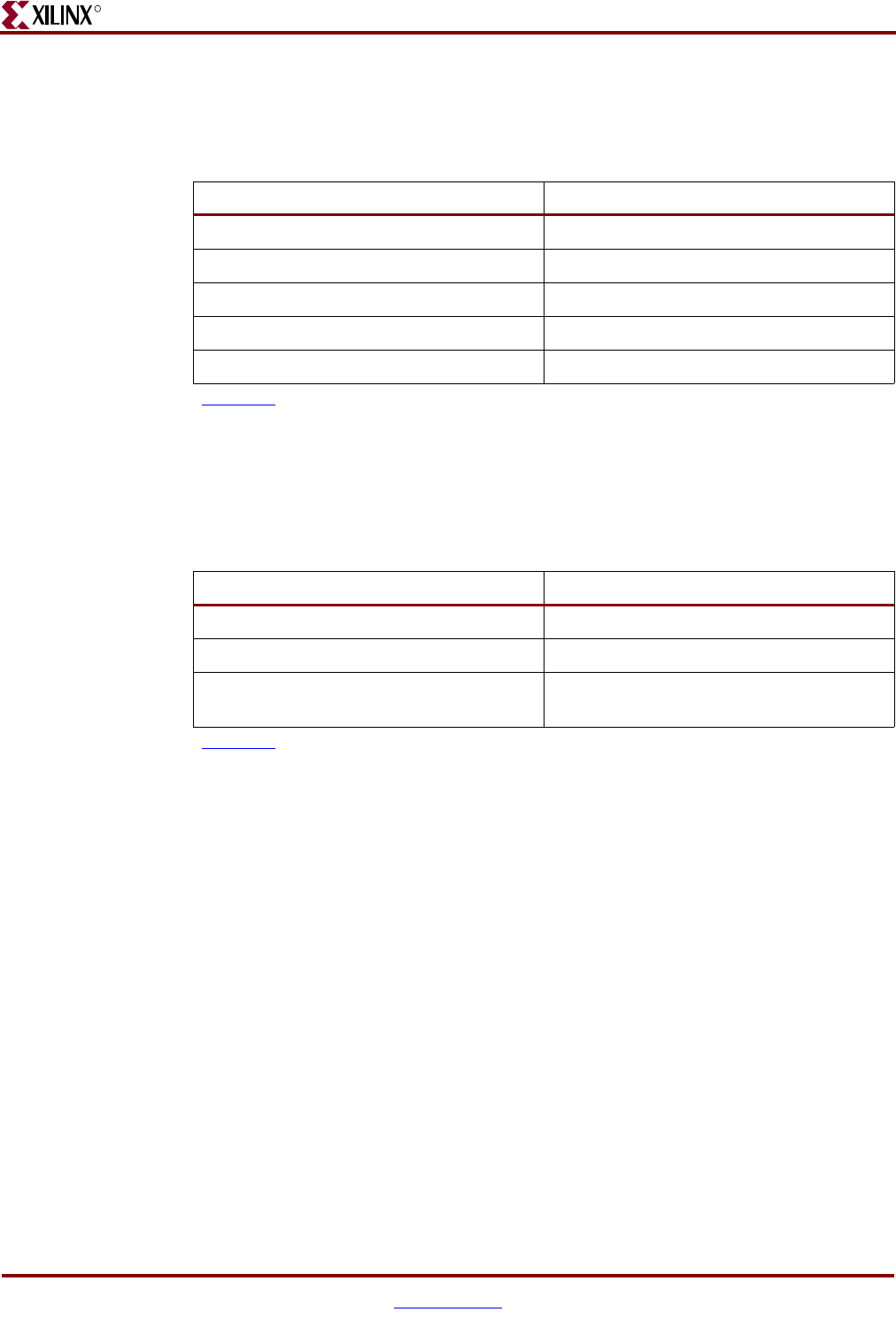

Table 3-14: Functional Directory

Name Description

simulate_dual_mti.do ModelSim simulation script.

simulate_dual_ncsim.sh Cadence IUS simulation script.

simulate_dual_vcs.sh VCS simulation script.

board_dual_rtl_x0*.f List of files for RTL simulations.

board_dual_rtl_x0*_ncv.f List of files for RTL simulations.

Back to Top

Table 3-15: Implement Directory

Name Description

implement_dual.sh Linux implementation script.

xst_dual.scr XST synthesis script.

xilinx_dual_pci_exp_*_lane_ep_inc.xst XST project file for 1-lane, 4-lane, and 8-

lane example design, respectively.

Back to Top