22 www.xilinx.com Endpoint Block Plus v1.8 for PCI Express

UG343 June 27, 2008

Chapter 3: Quickstart Example Design

R

<component name>/example_design

The example design directory contains the example design files provided with the core.

<component name>/implement

The implement directory contains the core implementation script files.

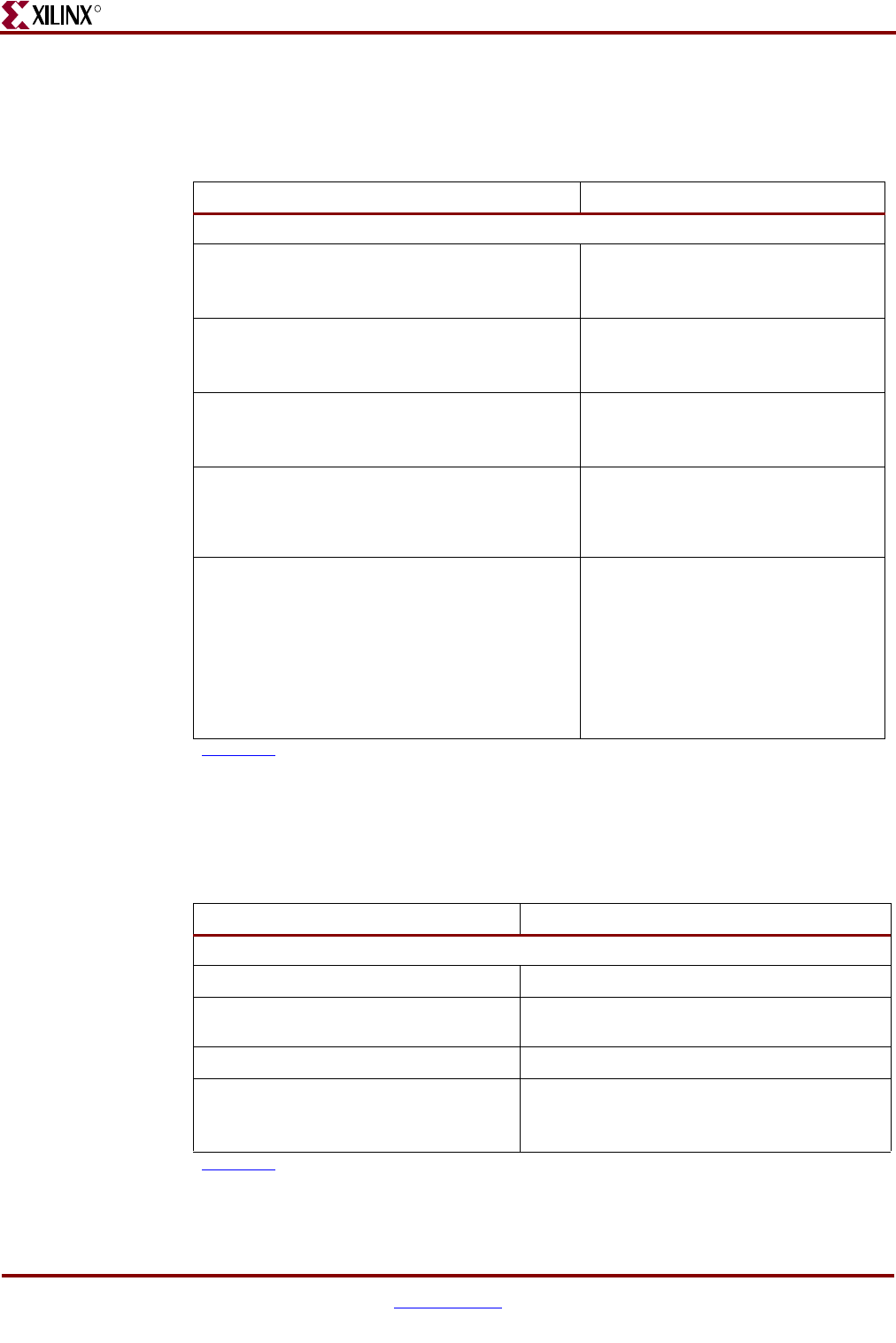

Table 3-4: Example Design Directory

Name Description

<project_dir>/<component_name>/example_design

pci_exp_8_lane_64b_ep.v

pci_exp_4_lane_64b_ep.v

pci_exp_1_lane_64b_ep.v

Verilog top-level port list, applicable

to the 8-lane, 4-lane, and 1-lane

endpoint design, respectively.

<filename>.ucf

Example design UCF. Filename

varies by lane-width, part, and

package selected.

xilinx_pci_exp_8_lane_ep_product.v

xilinx_pci_exp_4_lane_ep_product.v

xilinx_pci_exp_1_lane_ep_product.v

Enables Block Plus 8-lane, 4-lane,

and 1-lane cores, respectively, in the

test bench.

xilinx_pci_exp_8_lane_ep.v

xilinx_pci_exp_4_lane_ep.v

xilinx_pci_exp_1_lane_ep.v

xilinx_pci_exp_ep.vhd

Verilog or VHDL top-level PIO

example design files for 8-lane, 4-

lane, and 1-lane cores.

pci_exp_64b_app.v[hd]

EP_MEM.v[hd]

PIO.v[hd]

PIO_EP.v[hd]

PIO_EP_MEM_ACCESS.v[hd]

PIO_TO_CTRL.v[hd]

PIO_64.v

PIO_64_RX_ENGINE.v[hd]

PIO_64_TX_ENGINE.v[hd]

PIO example design files.

Back to Top

Table 3-5: Implement Directory

Name Description

<project_dir>/<component_name>/implement

xst.scr

XST synthesis script.

implement.bat

implement.sh

DOS and Linux implementation scripts.

synplify.prj

Synplify synthesis script.

xilinx_pci_exp_1_lane_ep_inc.xst

xilinx_pci_exp_4_lane_ep_inc.xst

xilinx_pci_exp_8_lane_ep_inc.xst

XST project file for 1-lane, 4-lane, and 8-lane

example design, respectively.

Back to Top