Endpoint Block Plus v1.8 for PCI Express www.xilinx.com 25

UG343 June 27, 2008

Dual Core Example Design

R

simulation/tests

The tests directory contains test definitions for the example test bench.

Dual Core Example Design

The dual core example design can be used as a starting point for designs with multiple

Virtex-5 FPGA PCI Express blocks. The dual core example design provides both Verilog

and VHDL source files, simulation scripts, and implementation files necessary to simulate

and implement a target design that uses two Virtex-5 PCI Express Blocks.

Although all Virtex-5 FXT FPGAs support multiple Endpoint Blocks, the dual core

example design is only generated by the CORE Generator when the PCI Express Endpoint

Block Plus for PCI Express is generated using the following device and package

combination(s):

Virtex 5 FX70T-FF1136 (XC5VFX70T-FF1136)

Note: The dual core example design may be used as a starting point for Virtex-5 FXT

FPGAs and package combinations not defined above; however, some FXT devices do not

support multiple 8-lane configurations. See “Chapter 5, Core Constraints” in the Endpoint

for PCI Express Block Plus User Guide for information about devices that support the 8-lane

configuration.

Figure 3-6 illustrates the dual core example design structure. The dual core example design

instantiates two Virtex-5 PCI Express Block cores with the same configuration (that is, lane

width, BAR configuration, and so forth). Designers using Virtex-5 PCI Express Blocks with

different configurations need to generate separate endpoint cores using the CORE

Generator and configure each as desired.

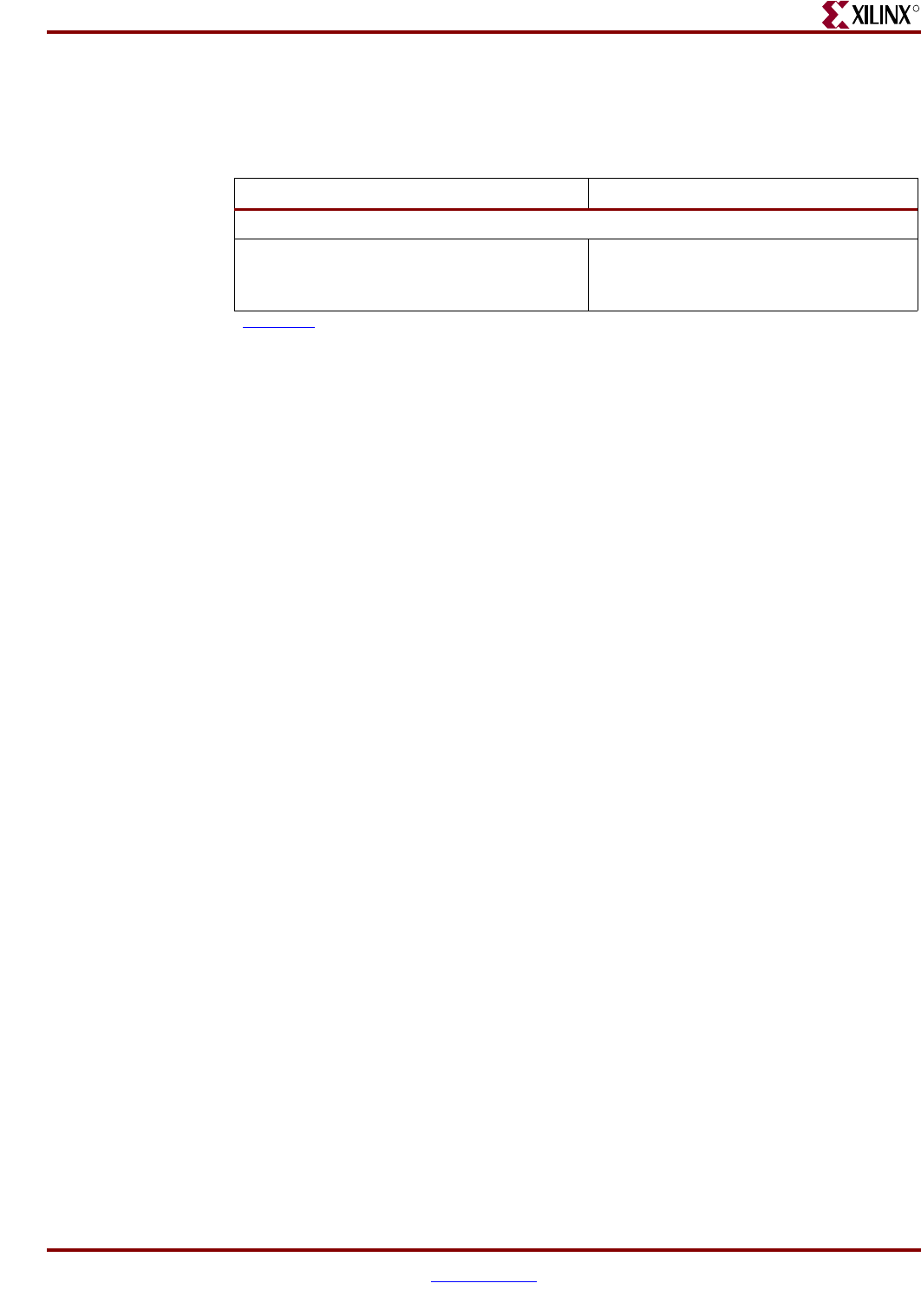

Table 3-10: Tests Directory

Name Description

<project_dir>/<component_name>/simulation/tests

pio_tests.v

sample_tests1.v

tests.v[hd]

Test definitions for example test bench.

Back to Top