CLOCK CIRCUIT S3C8245/P8245/C8249/P8249

7-2

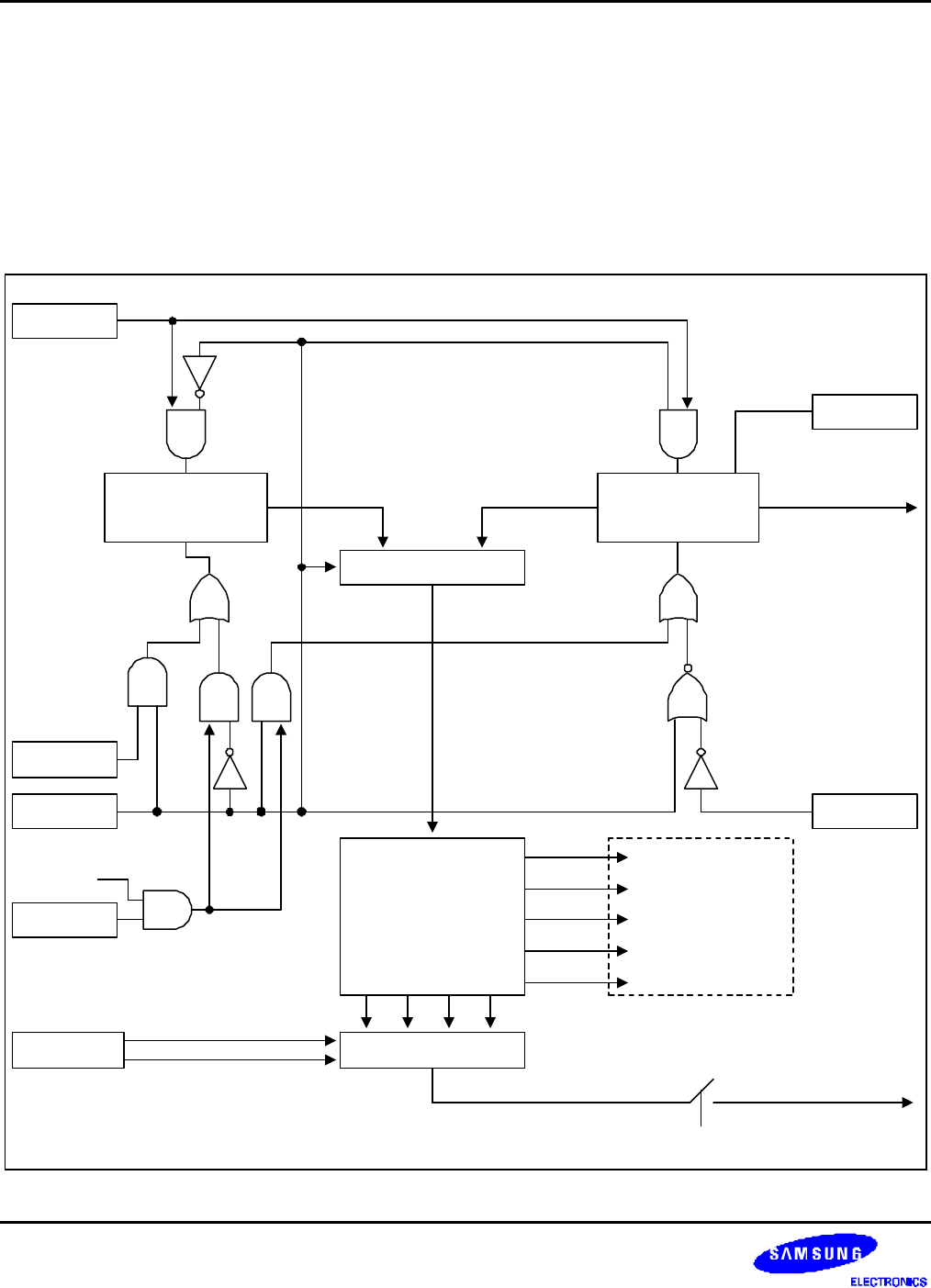

CLOCK STATUS DURING POWER-DOWN MODES

The two power-down modes, Stop mode and Idle mode, affect the system clock as follows:

— In Stop mode, the main oscillator is halted. Stop mode is released, and the oscillator is started, by a reset

operation or an external interrupt (with RC delay noise filter), and can be released by internal interrupt too when

the sub-system oscillator is running and watch timer is operating with sub-system clock.

— In Idle mode, the internal clock signal is gated to the CPU, but not to interrupt structure, timers and timer/

counters. Idle mode is released by a reset or by an external or internal interrupt.

1/8-1/4096

Frequency

Dividing

Circuit

Stop Release

Main-System

Oscillator

Circuit

Selector 1

f

x

f

xt

Stop

Driving Ability

Sub-system

Oscillator

Circuit

OSCCON.4

INT

OSCCON.0

OSCCON.3

OSCCON.2

Selector 2

STPCON

STOP OSC

inst.

f

xx

CLKCON.4-.3

CPU Clock

Stop

Watch Timer

Basic Timer

Timer/Counter

Watch Timer (fxx/128)

LCD Controller

A/D Converter

SIO

System Clock

IDLE Instruction

1/1 1/161/2 1/8

Figure 7-3. System Clock Circuit Diagram