S3C8245/P8245/C8249/P8249 CONTROL REGISTER

4-41

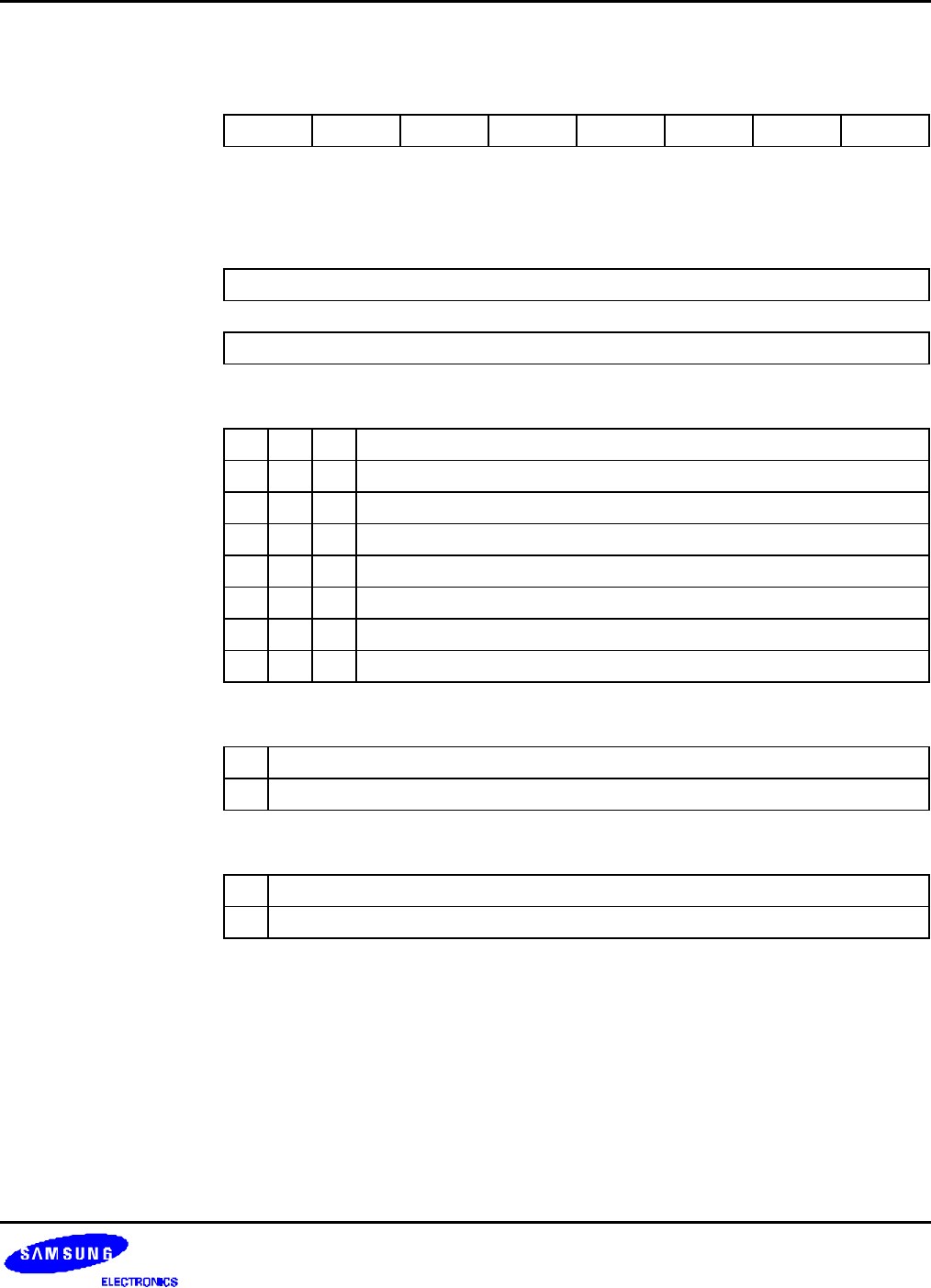

SYM — System Mode Register DEH Set 1

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

nRESET Value 0 – – x x x 0 0

Read/Write R/W – – R/W R/W R/W R/W R/W

Addressing Mode Register addressing mode only

.7 Not used, But you must keep "0"

.6–.5 Not used for the S3C8245/C8249

.4–.2

Fast Interrupt Level Selection Bits

(1)

0 0 0 IRQ0

0 0 1 IRQ1

0 1 0 IRQ2

0 1 1 IRQ3

1 0 0 IRQ4

1 0 1 IRQ5

1 1 0 IRQ6

1 1 1 IRQ7

.1

Fast Interrupt Enable Bit

(2)

0 Disable fast interrupt processing

1 Enable fast interrupt processing

.0

Global Interrupt Enable Bit

(3)

0 Disable all interrupt processing

1 Enable all interrupt processing

NOTES:

1. You can select only one interrupt level at a time for fast interrupt processing.

2. Setting SYM.1 to "1" enables fast interrupt processing for the interrupt level currently selected by SYM.2–SYM.4.

3. Following a reset, you must enable global interrupt processing by executing an EI instruction

(not by writing a "1" to SYM.0).