EL320.240-FA3 Operations Manual Page 11 of 25

Display Interface

The display supports five video interface modes: SGD timing as used on the

Planar EL320.240.36-HB (though with video data differences to denote colors)

and the four AMLCD timing modes used on Sharp and Kyocera QVGA color

displays (though using only two bits of red and green data). Four bits of data

per pixel are provided. The data is clocked to the display with a video clock,

VCLK. Frame and line synchronization is provided by the VS, HS and (if needed)

DE signals.

Video mode detection is performed automatically. The display evaluates the

timing of the incoming video approximately every 25 msec and will shift “on

the fly” between video modes as required.

The internal display controller utilizes a frame buffer to provide the display

with the appropriate modulation on a line by line and frame by frame basis to

implement the color generation, including frame dithering algorithms. Thus

the input frame rate and the display scan rate, in general, will not be the same

and will not be synchronous.

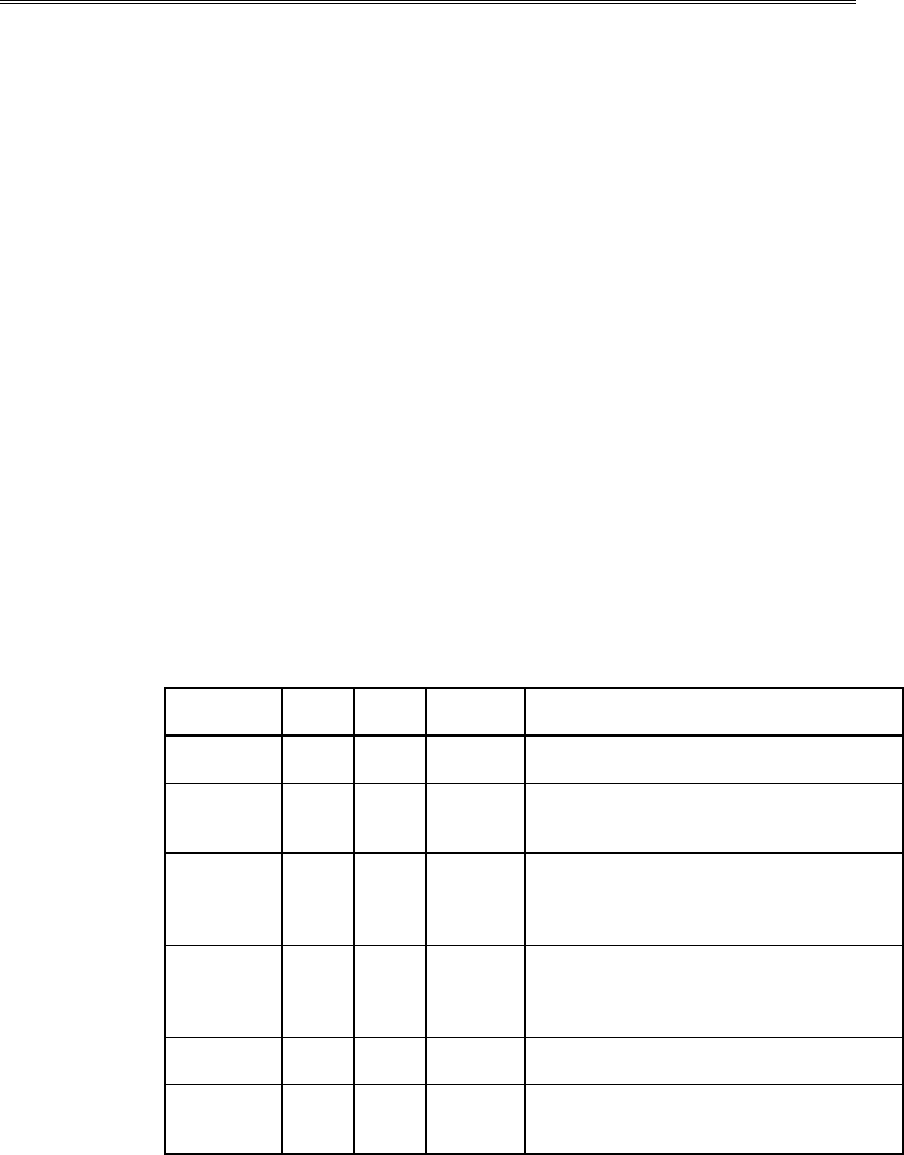

Video Mode Selection

Inputs LUM0 and LUM1 must be set to attain the desired video mode as shown

in the following table.

LUM0 and

LUM1 = 1?

V/Q

Input

DE

Input

Mode

Name

Mode Description

(refer to Video Mode Timing for details)

No 0 Active AMLCD,Q

VGA

AMLCD timing. DE determines the

horizontal location of data.

No 0 0 AMLCD,

QVGA,

Fixed

AMLCD timing. Horizontal start of valid

data is a predetermined number of VCLKs

from HS.

No 1 Active AMLCD,

VGA

AMLCD timing. Displays upper left

quadrant of a VGA (640x480) input signal

with DE determining the horizontal

location of data.

No 1 0 AMLCD,

VGA,

Fixed

AMLCD timing. Displays upper left

quadrant of a VGA (640x480) input signal

with the horizontal start of valid data

predetermined.

No X 1 SGD SGD timing. Horizontal start of valid data is

the first VCLK after HS.

Yes X X Self test Displays various patterns at the maximum

refresh rate regardless of video input data.

Useful for verifying display functionality.

Note:1) DE is considered active if more than eight logic transitions are detected

2) SGD mode is similar to that of the Planar EL320.240.36 and EL320.240-HB

displays but with required changes to the video data content to represent color

3) The AMLCD modes are compatible with those found on the following QVGA

displays though the video data content of 4 bits/pixel is a subset of the typical

18 bits/pixel: Sharp LQ057Q3DC12, Sharp LQ057Q3DC02, Kyocera

TCG057QV1AC