Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

RESET

2003 Dec 8 73

9. RESET

The P1.5/RST pin can function as either an active low reset input or as a digital input, P1.5. The RPE (Reset Pin Enable) bit in

UCFG1, when set to 1, enables the external reset input function on P1.5. When cleared, P1.5 may be used as an input pin.

NOTE: During a power-on sequence, The RPE selection is overriden and this pin will always functions as a reset input. An

external circuit connected to this pin should not hold this pin low during a Power-on sequence as this will keep the device in reset.

After power-on this input will function either as an external reset input or as a digital input as defined by the RPE bit. Only a power-

on reset will temporarily override the selection defined by RPE bit. Other sources of reset will not override the RPE bit.

NOTE: During a power cycle, V

DD

must fall below V

POR

(see "DC electrical characteristics" in the datasheet) before pwoer is

reapplied, in order to ensure a power-on reset.

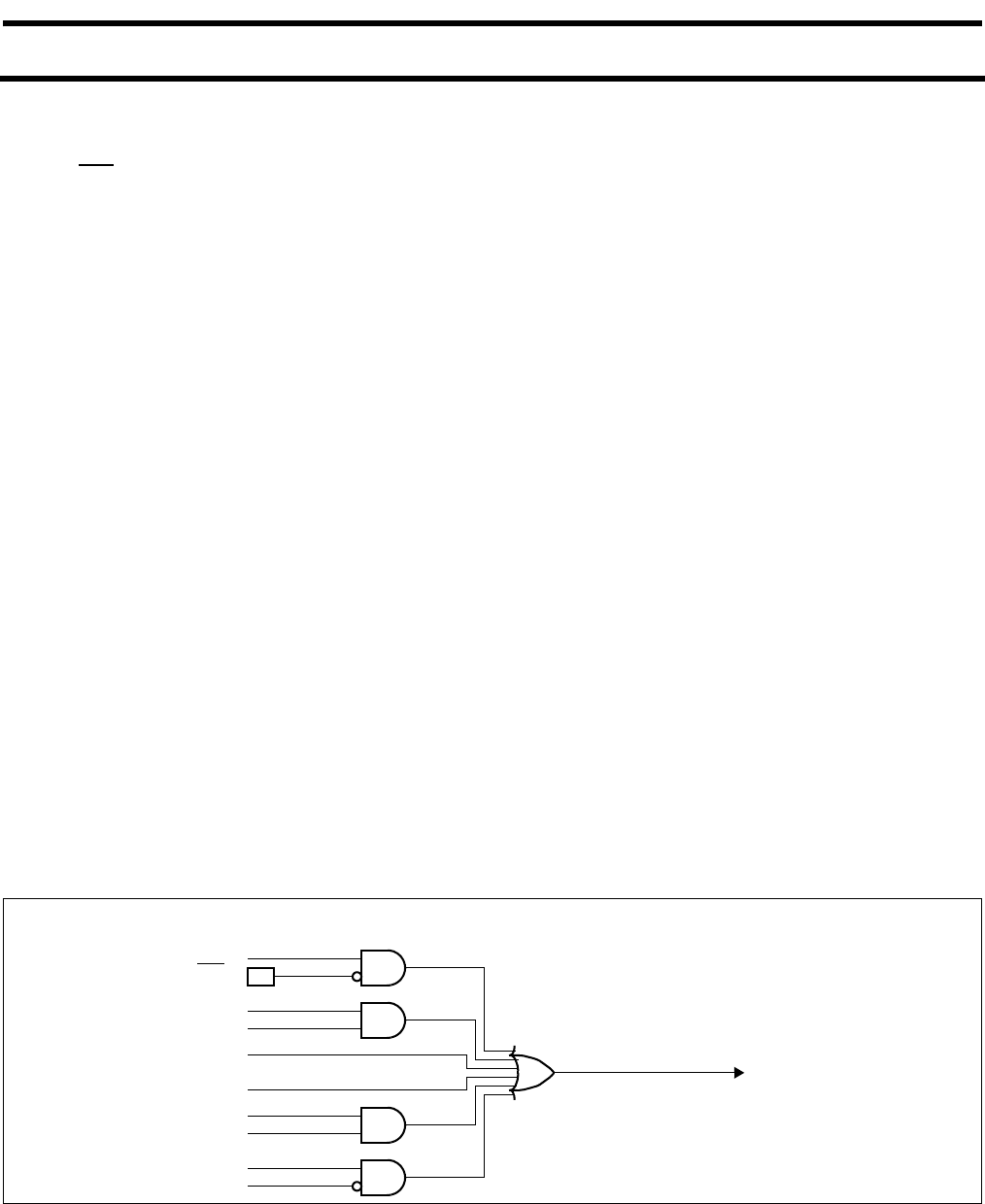

Reset can be triggered from the following sources (see Figure 9-1):

• External reset pin (during power-on or if user configured via UCFG1);

• Power-on Detect;

• Brownout Detect;

• Watchdog Timer;

• Software reset;

• UART break-character detect reset. (P89LPC903)

For every reset source, there is a flag in the Reset Register, RSTSRC. The user can read this register to determine the most

recent reset source. These flag bits can be cleared in software by writing a ’0’ to the corresponding bit. More than one flag bit

may be set:

• During a power-on reset, both POF and BOF are set but the other flag bits are cleared.

• For any other reset, any previously set flag bits that have not been cleared will remain set.

Power-On reset code execution

The P89LPC901/902/903 contains two special Flash elements: the BOOT VECTOR and the Boot Status Bit. Following reset,

the P89LPC901/902/903 examines the contents of the Boot Status Bit. If the Boot Status Bit is set to zero, power-up execution

starts at location 0000H, which is the normal start address of the user’s application code. When the Boot Status Bit is set to a

one, the contents of the Boot Vector is used as the high byte of the execution address and the low byte is set to 00H. The fac-

tory default setting is 00H. A UART break-detect reset (P89LPC903) will have the same effect as a non-zero Status Bit.

Figure 9-1: Block Diagram of Reset

Chip Reset

RPE (UCFG1.6)

Watchdog Timer Reset

Software Reset SRST (AUXR1.3)

Power-on Detect

RST

Pin

WDTE (UCFG1.7)

UART Break Detect

EBRR (AUXR1.6)

Brownout Detect Reset

BOPD (PCON.5)