Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

WATCHDOG TIMER

2003 Dec 8 87

Watchdog Timer in Timer Mode

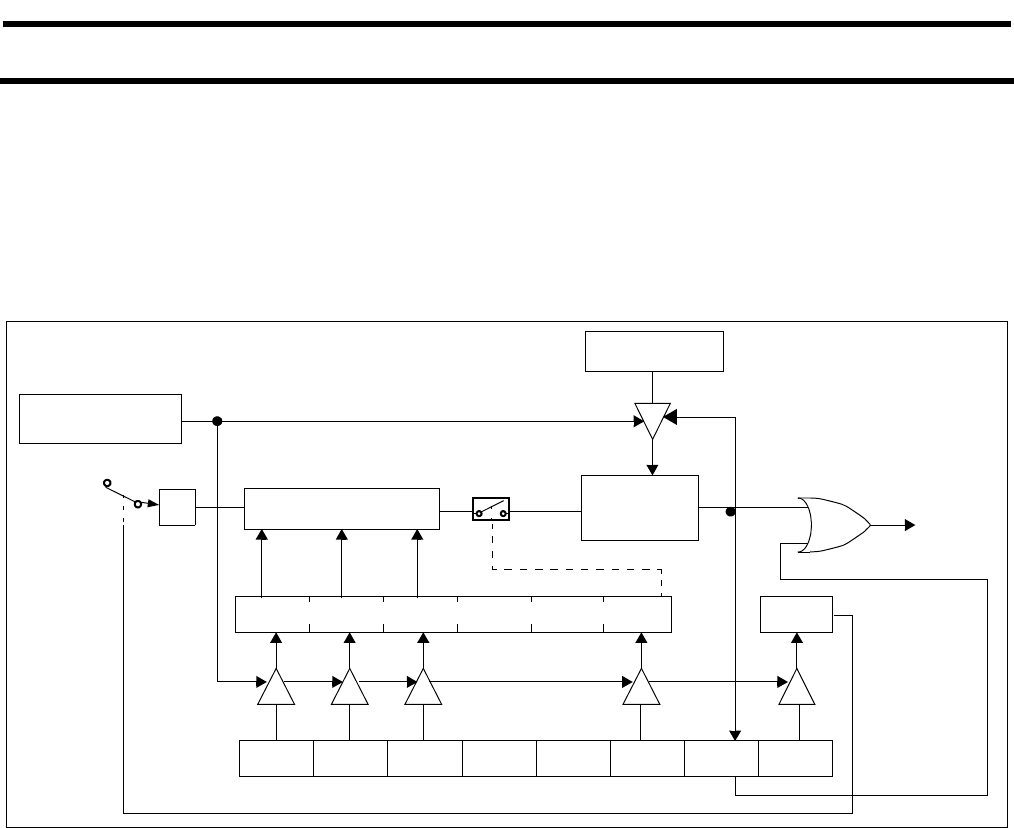

Figure 12-4 shows the Watchdog Timer in Timer Mode. In this mode, any changes to WDCON are written to the shadow register

after one watchdog clock cycle. A watchdog underflow will set the WDTOF bit. If IEN0.6 is set, the watchdog underflow is enabled

to cause an interrupt. WDTOF is cleared by writing a '0' to this bit in software. When an underflow occurs, the contents of WDL

is reloaded into the down counter and the watchdog timer immediately begins to count down again.

A feed is necessary to cause WDL to be loaded into the down counter before an underflow occurs. Incorrect feeds are ignored

in this mode.

Figure 12-4: Watchdog Timer in Timer Mode (WDTE = 0)

Power down operation

The WDT oscillator will continue to run in power down, consuming approximately 50uA, as long as the WDT oscillator is selected

as the clock source for the WDT. Selecting PCLK as the WDT source will result in the WDT oscillator going into power down

with the rest of the device (see section "Watchdog Clock Source", below ). Power down mode will also prevent PCLK from running

and therefore the watchdog is effectively disabled.

Watchdog Clock Source

The watchdog timer system has an on-chip 400KHz oscillator. The watchdog timer can be clocked from either the watchdog

oscillator or from PCLK (refer to Figure 12-1) by configuring the WDCLK bit in the Watchdog Control Register WDCON. When

the watchdog feature is enabled, the timer must be fed regularly by software in order to prevent it from resetting the CPU.

After changing WDCLK (WDCON.0), switching of the clock source will not immediately take effect. As shown in Figure 12-3, the

selection is loaded after a watchdog feed sequence. In addition, due to clock synchronization logic, it can take two old clock cycles

before the old clock source is deselected, and then an additional two new clock cycles before the new clock source is selected.

Since the prescaler starts counting immediately after a feed, switching clocks can cause some inaccuracy in the prescaler count.

The inaccuracy could be as much as 2 old clock source counts plus 2 new clock cycles.

8-Bit Down

Counter

MOV WFEED1, #0A5H

MOV WFEED2, #05AH

WDL (C1H)

PRE2 PRE1 PRE0 WDRUN WDTOF WDCLK

SHADOW

REGISTER FOR

WDCON

WDCON(A7H)

PRESCALER

Interrupt

control register

Watchdog

Oscillator

CLK

÷32