Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

UART (P89LPC903)

2003 Dec 8 67

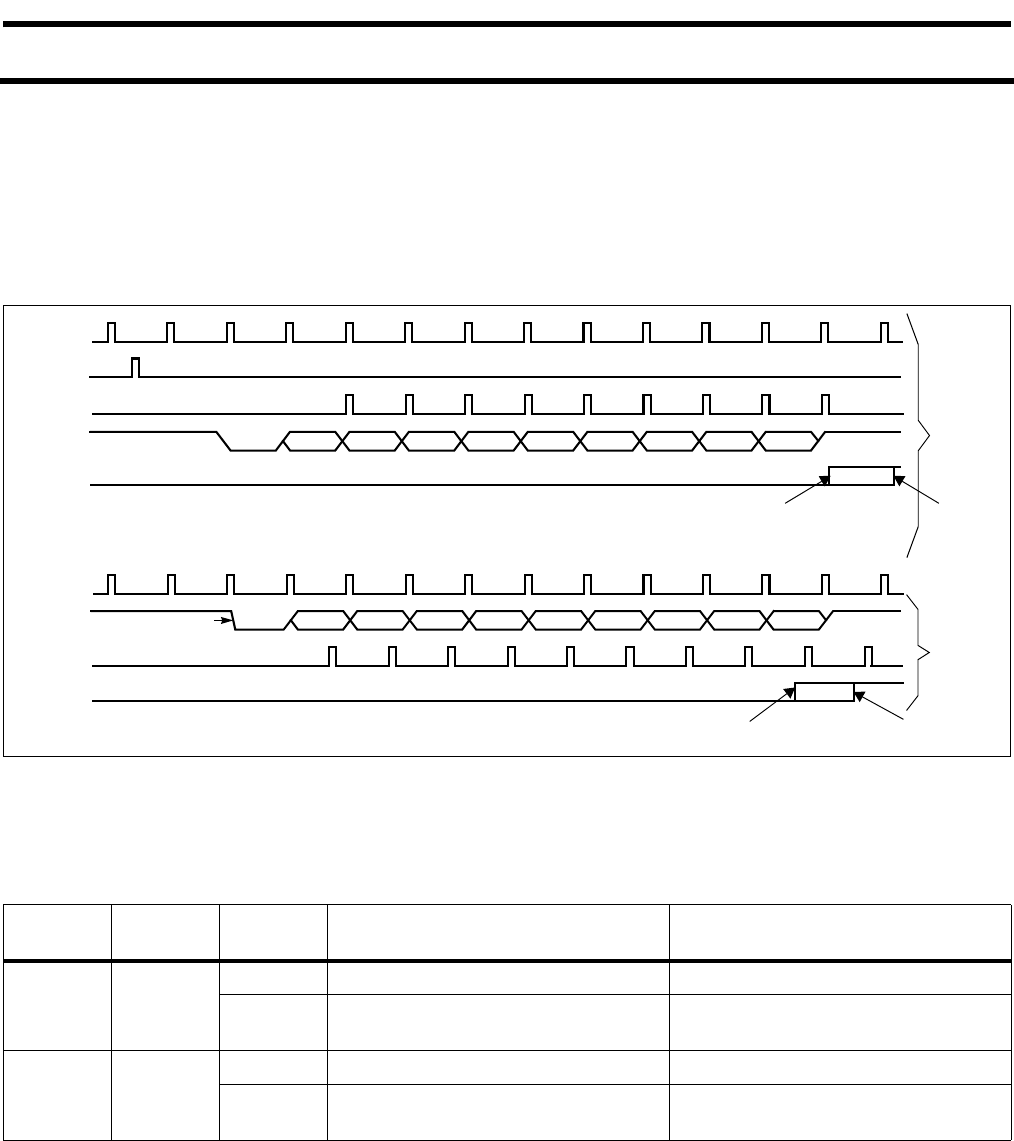

More About UART Modes 2 and 3

Reception is the same as in Mode 1.

The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the

final shift pulse is generated. (a) RI = 0, and (b) Either SM2 = 0, or the received 9th data bit = 1. If either of these conditions is

not met, the received frame is lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the

first 8 data bits go into SBUF.

Figure 8-7: Serial Port Mode 2 or 3 (Only Single Transmit Buffering Case Is Shown)

Framing Error and RI in Modes 2 and 3 with SM2 = 1

If SM2 = 1 in modes 2 and 3, RI and FE behave as in the following table.

Break Detect

A break is detected when 11 consecutive bits are sensed low and is reported in the status register (SSTAT). For Mode 1, this

consists of the start bit, 8 data bits, and two stop bit times. For Modes 2 & 3, this consists of the start bit, 9 data bits, and one stop

bit. The break detect bit is cleared in software or by a reset. The break detect can be used to reset the device. This occurs if the

UART is enabled and the the EBRR bit (AUXR1.6) is set and a break occurs.

Mode

PCON.6

(SMOD0)

RB8 RI FE

20

0 No RI when RB8 = 0 Occurs during STOP bit

1

Similar to Figure 8-7, with SMOD0 = 0, RI

occurs during RB8, one bit before FE

Occurs during STOP bit

31

0 No RI when RB8 = 0 Will NOT occur

1

Similar to Figure 8-7, with SMOD0 = 1, RI

occurs during STOP bit

Occurs during STOP bit

Table 8-3: FE and RI when SM2 = 1 in Modes 2 and 3.

Transmit

Start Bit Stop Bit

TX Clock

Write to SBUF

Shift

TxD

TI

D0 D1 D5D2 D6D3 D4 D7

Receive

RX Clock

Shift

RI

Start Bit

Stop Bit

RxD

D0 D1 D5D2 D6D3 D4 D7

÷ 16 Reset

TB8

RB8

INTLO = 0

INTLO = 1

SMOD0 = 0

SMOD0 = 1