Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

WATCHDOG TIMER

2003 Dec 8 84

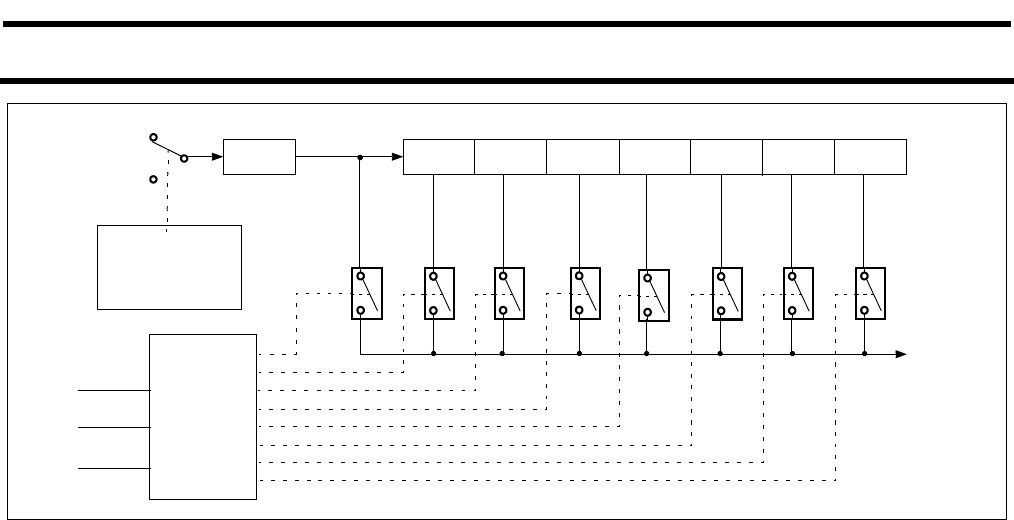

Figure 12-1: Watchdog Prescaler

Feed Sequence

The watchdog timer control register and the 8-bit down counter (Figure 12-3) are not directly loaded by the user. The user writes

to the WDCON and the WDL SFRs. At the end of a feed sequence, the values in the WDCON and WDL SFRs are loaded to the

control register and the 8-bit down counter. Before the feed sequence, any new values written to these two SFRs will not take

effect. To avoid a watchdog reset, the watchdog timer needs to be fed (via a special sequence of software action called the feed

sequence) prior to reaching an underflow.

To feed the watchdog, two write instructions must be sequentially executed successfully. Between the two write instructions, SFR

reads are allowed, but writes are not allowed. The instructions should move A5H to the WFEED1 register and then 5AH to the

WFEED2 register. An incorrect feed sequence will cause an immediate watchdog reset. The program sequence to feed the

watchdog timer is as follows:

CLR EA ; disable interrupt

MOV WFEED1,#0A5h ; do watchdog feed part 1

MOV WFEED2,#05Ah ; do watchdog feed part 2

SETB EA ; enable interrupt

This sequence assumes that the P89LPC901/902/903 interrupt system is enabled and there is a possibility of an interrupt request

occuring during the feed sequence. If an interrupt was allowed to be serviced and the service routine contained any SFR writes,

it would trigger a watchdog reset. If it is known that no interrupt could occur during the feed sequence, the instructions to disable

and re-enable interrupts may be removed.

In watchdog mode (WDTE = 1), writing the WDCON register must be IMMEDIATELY followed by a feed sequence to load the

WDL to the 8-bit down counter, and the WDCON to the shadow register. If writing to the WDCON register is not immediately

followed by the feed sequence, a watchdog reset will occur.

For example: setting WDRUN = 1:

MOV ACC,WDCON ; get WDCON

SETB ACC.2 ; set WD_RUN=1

MOV WDL,#0FFh ; New count to be loaded to 8-bit down counter

CLR EA ; disable interrupt

MOV WDCON,ACC ; write back to WDCON (after the watchdog is enabled, a feed must occur

; immediately)

PRE2

PRE1

PRE0

DECODE

÷2 ÷2 ÷2 ÷2 ÷2 ÷2 ÷2

÷32 ÷64 ÷128 ÷256 ÷512 ÷1024 ÷2048 ÷4096

000

001

010

011

100

101

110

111

TO

WATCHDOG

DOWN

COUNTER

(after one

prescaler

count delay

Watchdog

Oscillator

WDCLK after a

watchdog feed

sequence

PCLK

÷32