Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

UART (P89LPC903)

2003 Dec 8 69

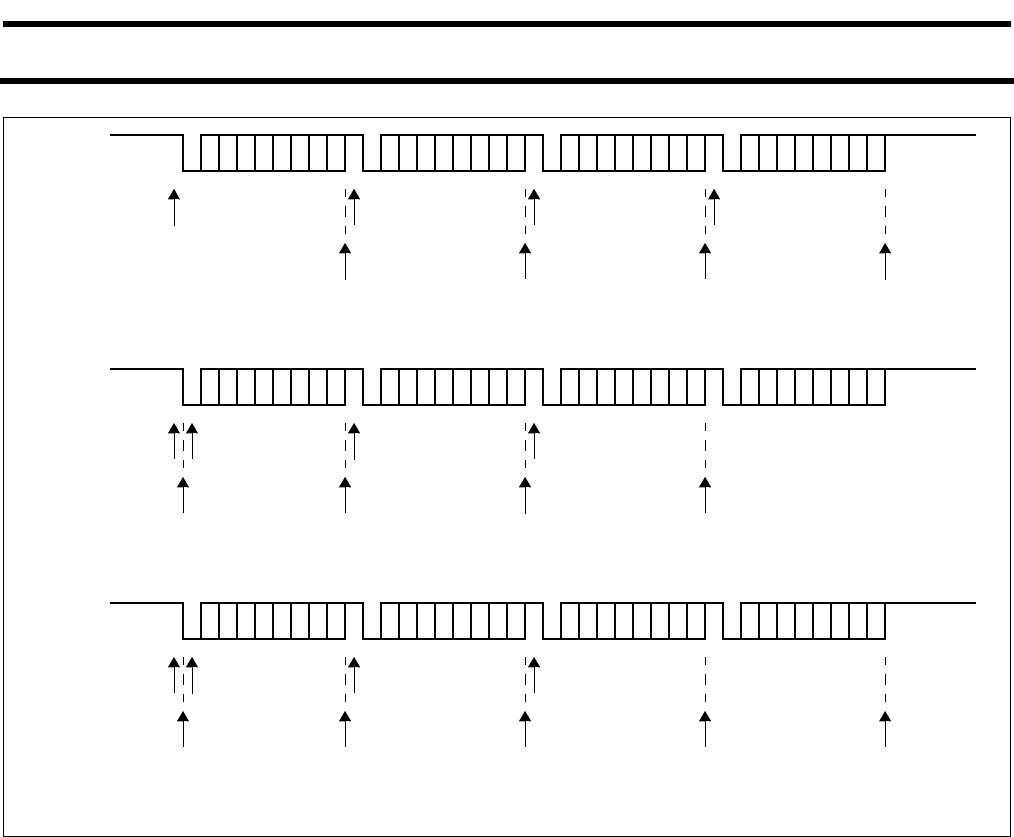

Figure 8-8: Transmission with and without Double Buffering

The 9th Bit (Bit 8) in Double Buffering (Modes 1, 2 and 3)

If double buffering is disabled (DBMOD, i.e. SSTAT.7 = 0), TB8 can be written before or after SBUF is written, provided TB8 is

updated before that TB8 is shifted out. TB8 must not be changed again until after TB8 shifting has been completed, as indicated

by the Tx interrupt.

If double buffering is enabled, TB8 MUST be updated before SBUF is written, as TB8 will be double-buffered together with SBUF

data. The operation described in the section "Transmit Interrupts with Double Buffering Enabled (Modes 1, 2 and 3)" becomes

as follows:

1. The double buffer is empty initially.

2. The CPU writes to TB8.

3. The CPU writes to SBUF.

4. The SBUF/TB8 data is loaded to the shift register and a Tx interrupt is generated immediately.

5. If there is more data, go to 7, else continue on 6.

6. If there is no more data, then:

- If DBISEL is ’0’, no more interrupt will occur.

- If DBISEL is ’1’ and INTLO is ’0’, a Tx interrupt will occur at the beginning of the STOP bit of the data currently in the shifter

(which is also the last data).

TxD

Write to

SBUF

Tx Interrupt

Single Buffering (DBMOD/SSTAT.7 = 0), Early Interrupt (INTLO/SSTAT.6 = 0) is Shown

TxD

Write to

SBUF

Tx Interrupt

Double Buffering (DBMOD/SSTAT.7 = 1), Early Interrupt (INTLO/SSTAT.6 = 0) is Shown, No End-

ing Tx Interrupt (DBISEL/SnSTAT.4 = 0)

TxD

Write to

SBUF

Tx Interrupt

Double Buffering (DBMOD/SSTAT.7 = 1), Early Interrupt (INTLO/SSTAT.6 = 0) is Shown, With

Ending Tx Interrupt (DBISEL/SSTAT.4 = 1)