104

CHAPTER 5 ACCESS BETWEEN CPU MODULES

AND OTHER MODULES

This chapter describes the access between CPU modules and other modules (I/O modules and intelligent function

modules).

5.1 Access to Controlled Modules

In a multiple CPU system, CPU modules access I/O modules and intelligent function modules in the same way as in a

single CPU system. (CPU modules refresh input (X) and output (Y) data, and read/write data from/to the buffer

memory of intelligent function modules.)

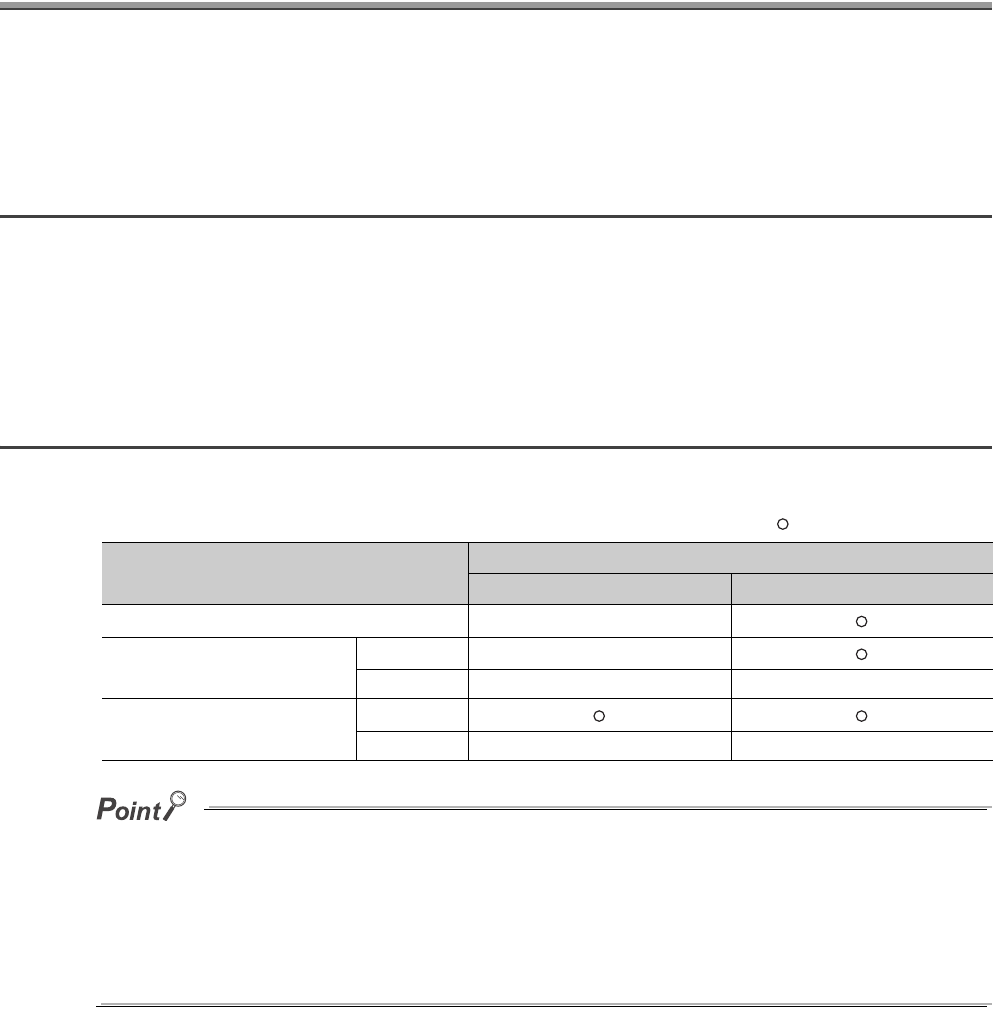

5.2 Access to Non-controlled Modules

Access to non-controlled modules is restricted as shown below.

: Accessible ×: Inaccessible

● The on/off data of the I/O modules, I/O combined modules, and intelligent function modules controlled by other CPU

modules can be used as an interlock of the host CPU module or to check the status of output to external devices

controlled by other CPU modules.

● The on/off status of input (X) and output (Y) can be read by setting "I/O Sharing When Using Multiple CPUs" in PLC

parameter. (The on/off status cannot be written to the devices.)

● Data in the buffer memory of intelligent function modules can be read regardless of the "I/O Sharing When Using Multiple

CPUs" setting. (The data cannot be written to the buffer memory.)

Access target

"I/O Sharing When Using Multiple CPUs" in PLC parameter

Disabled (not checked) Enabled (checked)

Input (X) ×

Output (Y)

Read ×

Write × ×

Buffer memory of an intelligent

function module

Read

Write × ×