134

Ex.

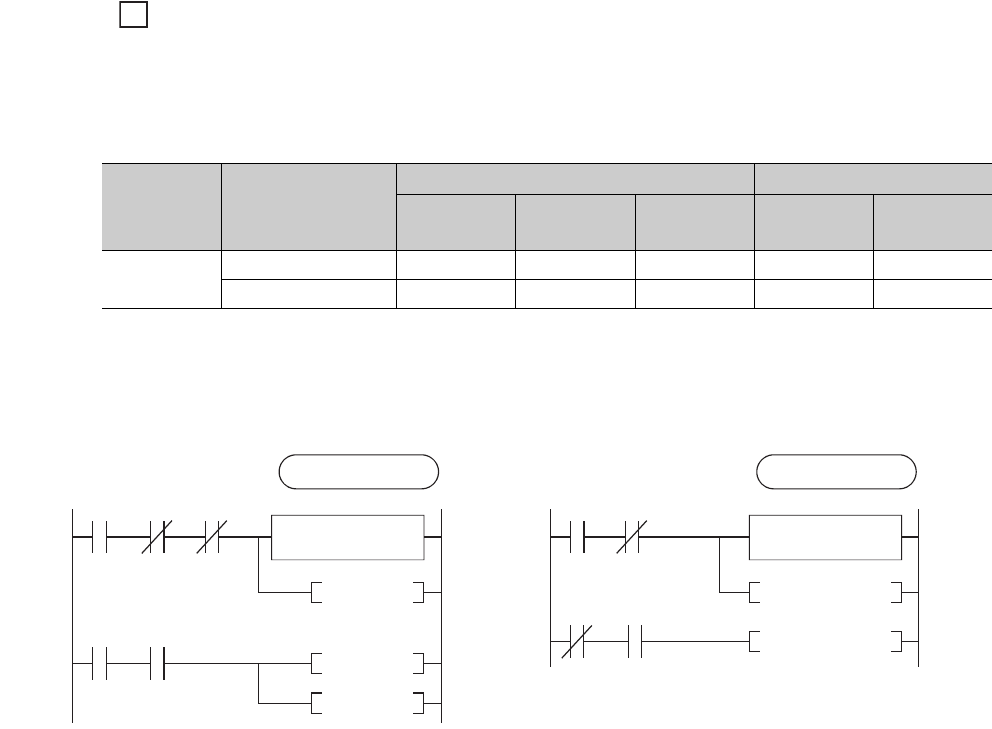

Auto refresh between QCPUs

The following are the program examples for the High Performance model QCPUs when PLC parameters

("Communication Area Setting (Refresh Setting)" of "Multiple CPU Setting") are set as shown below.

[Parameter setting]

Use D0.0 as an interlock device of CPU No.1 (data setting complete bit) and D1024.0 as an interlock

device of CPU No.2 (receive data processing complete bit).

Program example (sending side) (CPU No.1)Program example (receiving side) (CPU No.2)

1) CPU No.1 creates send data.

2) CPU No.1 turns on the data setting complete bit.

(Auto refresh execution)

3) CPU No.2 detects the completion of send data setting.

4) CPU No.2 performs receive data processing.

5) CPU No.2 turns on the receive data processing complete bit.

(Auto refresh execution)

6) CPU No.1 detects the completion of the receive data processing, and turns off the data setting

complete bit.

(Auto refresh execution)

7) CPU No.2 detects the off status of the data setting complete bit, and turns off the receive data

processing complete bit.

Setting No.

("Change

Screens")

PLC

CPU Specific Send Range PLC Side Device

Points Start End Start End

Setting 1

PLC No.1 1024 0000 03FF D0 D1023

PLC No.2 1024 0000 03FF D1024 D2047

D1024.0D0.0MO

(Sending side

(CPU No.1))

6)

3)

1) 4)

2) 5)

D1024.0D0.0

D1024.0D0.0

(Receiving side

(CPU No.2))

7)

D1024.0D0.0

SET D0.0

RST MO

RST D0.0

SET D1024.0

RST D1024.0

Write

command

Setting the send

data to D0 to D1023

Reading the receive

data from D0 to D1023