153

CHAPTER 6 COMMUNICATIONS AMONG CPU MODULES

6

6.1 Communications Using the CPU Shared Memory

6.1.3 Communications by programs using the CPU shared memory

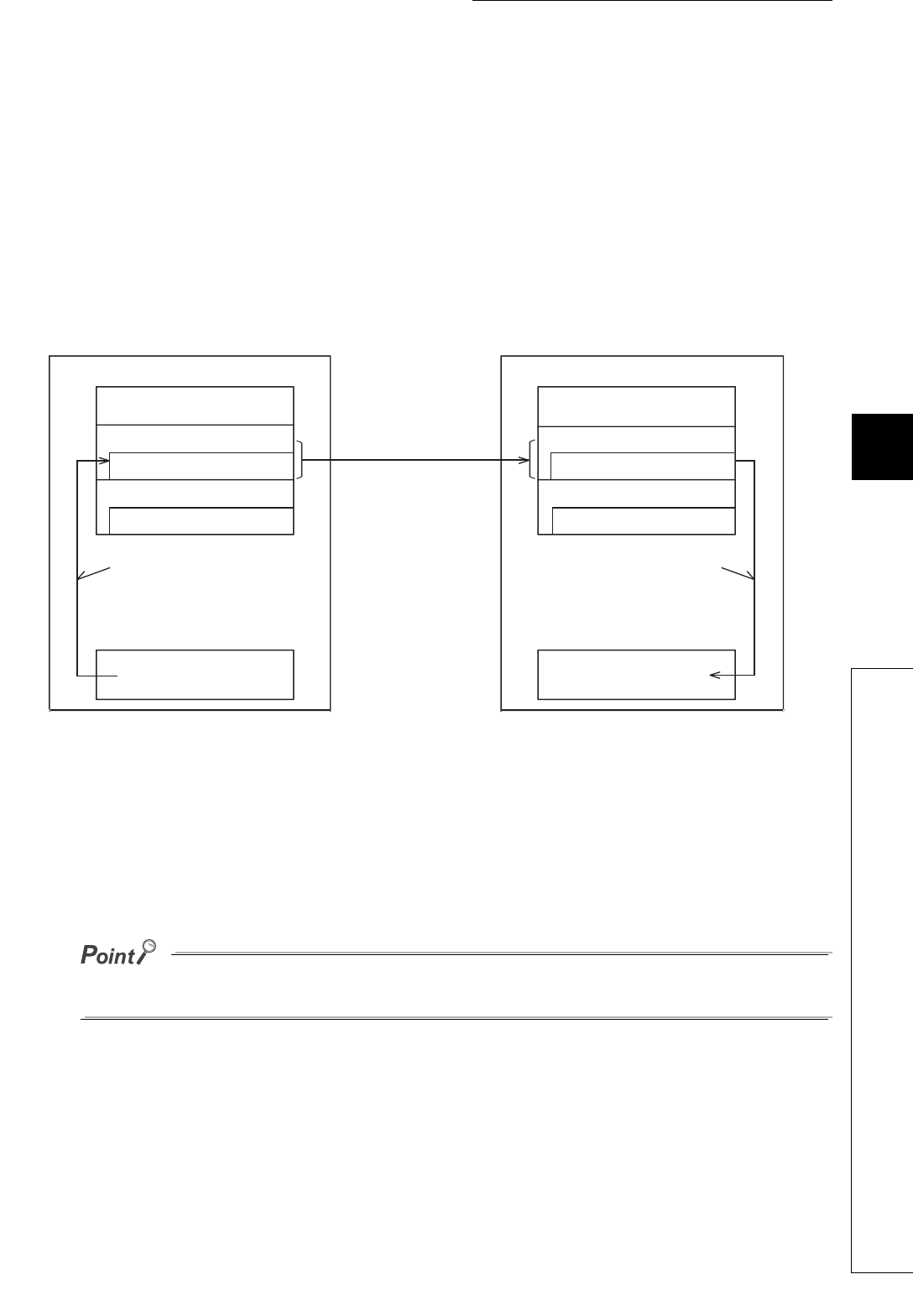

(5) Overview (when the user setting area in the multiple CPU high speed

communication area is used)

The data written to the multiple CPU high speed transmission area of the host CPU module by a write instruction

is sent to other CPU modules at regular intervals. Other CPU modules read the receive data by a read

instruction.

Unlike the auto refresh using the CPU shared memory, the up-to-date data at the time of an instruction execution

can be read directly.

The following shows the operation when data written to the CPU shared memory of CPU No.1 by a write

instruction is read by CPU No.2 by a read instruction.

• Procedure for CPU No.2 to read device data of CPU No.1

1) CPU No.1 writes data in the user setting area of the multiple CPU high speed transmission area of its own

by the write instruction.

2) CPU No.1 sends the stored data in the multiple CPU high speed transmission area to that of CPU No.2.

3) CPU No.2 reads the received data and stores the data in the specified device by the read instruction.

For the write/read instructions, refer to Page 151, Section 6.1.3 (2).

The delay time of data communications by programs using the user setting area in the multiple CPU high speed

transmission area is from 0.09ms to 1.80ms.

CPU No.1

CPU shared memory

CPU No.2

CPU shared memory

1) 3)

2)

Multiple CPU high speed

transmission area of CPU No.1

User setting area

Multiple CPU high speed transmission

area of CPU No.2

User setting area

Data are written by the write

instruction.

Execution of

write instruction

Multiple CPU high speed

transmission area of CPU No.1

User setting area

Multiple CPU high speed

transmission area of CPU No.2

User setting area

Data are read by the read

instruction.

Execution of

read instruction

Data are sent to CPU

No.2.